基于PCIe总线的超高速信号采集卡的设计

4.2 系统采集时序控制

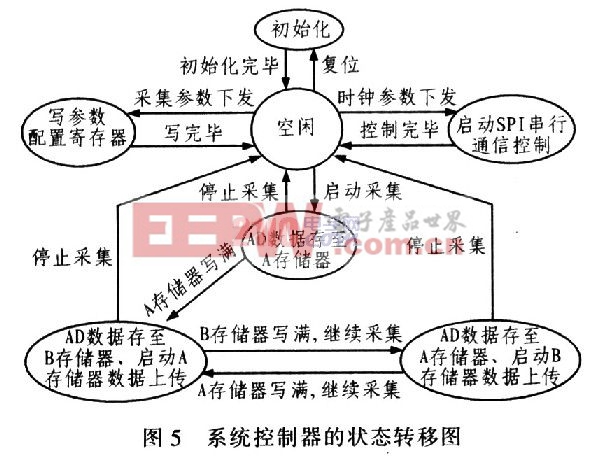

系统控制模块完成采集数据上传、主机命令的下发和执行:系统控制采用有限状态机的控制方式,如图5所示。当系统上电后控制器默认进入初始化状态,完成默认参数的配置,包括采样频率、采样深度、触发方式、时钟源的选择、模拟输入的量程和耦合方式等,初始化执行完毕后进入空闲状态,等待接收主机命令和执行操作;当接收到启动采集的命令后,控制器首先将AD输入的数据总线挂接在内存A数据总线上,并启动内存A的DDR2控制器执行写操作;当内存A存储到软件设定的深度或存满时,切换AD输入的数据总线挂接在内存B数据总线上,启动内存B的DDR2控制器执行写入操作,同时通过DMA中断通知主机,等待主机上传内存A中的数据;如此反复循环工作,直到收到主机停止采集

的命令再返回到空闲状态。本文引用地址://m.amcfsurvey.com/article/195369.htm

5 结束语

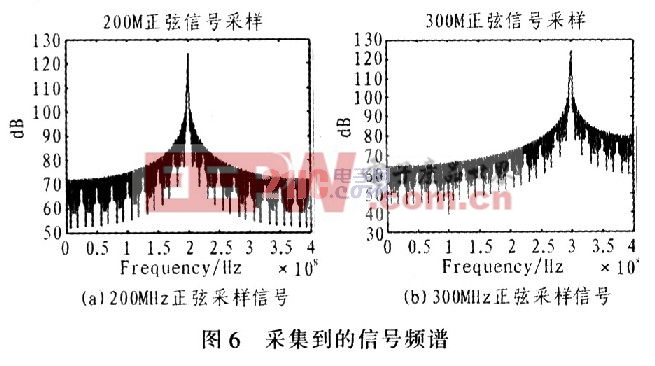

本文介绍了基于PCIe高速串行总线和FPGA控制器的超高速信号采集卡的设计技术,实现了不间断采样和连续传输等关键技术。采集到的信号频谱见图6。该采集卡已应用于某雷达侦察和干扰系统,取得了良好的效果,具有重要的实用价值。

评论