高性能手持示波表低功耗设计中的关键技术

方案二:多片相对低速ADC拼合实现500MSaps。针对要求,这里可通道选择两片AD9481交替采集实现,该方案需提供两对相差180度的250MSaps的时钟,共四路时钟,这种情况,完全可以由FPGA直接提供实现。该方案最大特点在于时钟灵活性高,比如在慢速时基档位下,可以在FPGA中灵活设置不同频率的采样时钟,达到动态减小功耗的目的。

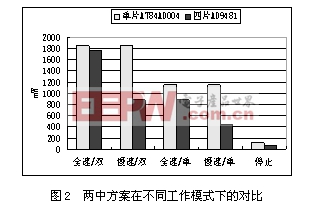

根据示波表工作的不同状态,对两种方案的ADC部分功耗情况进行了对比,如表2所示。

其中Po是指采用单片AT84AD004因为需要的额外时钟器件而带来的功耗,大约200mW,全速/双通道是指示波表双通道都处于运行状态,且ADC工作在最高采样率500MSaps情况下,慢速是指示波表工作在慢时基档位,ADC的工作采样率 250MSaps。

两种方案的ADC方案功耗对比如图2所示:

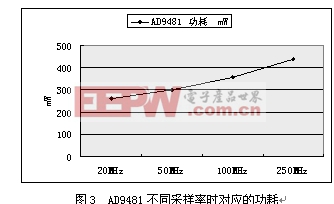

显然,方案二在各种工作模式下的功耗都低于方案一。实际上,ADC全速采样所对应的时基档位个数通常不到时基档位总个数的30%,慢速时基档位占大部分;而用户大多数时间是使用一个通道进行测量,单通道使用占主要部分;所以“慢速/双通道”、 “全速/单通道”、“慢速/单通道”模式是主要工作状态,而在“慢速/双通道”、“慢速/单通道”模式下,方案二的功耗远远低于方案一。另外,实际上 ADC的功耗与采样率是成正比关系,当系统采样率在小于250MSaps的时候,ADC功耗还有减小的空间,此时可以通过FPGA灵活的改变送到ADC的采样时钟频率来实现。图3是AD9481在不同采样率情况下的功耗情况,可以看到当采样时钟为20Msaps情况下,功耗已经低于300mW。

所以,在拼合采样质量满足要求的情况,手持示波表中数据采集方案采用多片ADC拼合采集方案更具有高的灵活性,功耗更低。

在实际方案验证过程中,对两种方案的采样质量进行了对比测试,在最高采样率500MSaps情况下,方案二通过FPGA产生两路相位差180度的250MHz采样时钟分别送到两片ADC中,进行交替采样,得到的有效位数仅比方案一有的效位数低约0.3bit,完全满足示波表的应用要求,而由此换来的低功耗则是非常可观的。

4、其他低功耗策略

在设计示波表过程中,除以上讨论的数据采集系统低功耗设计及注意电源模块高效率外,做好以下几方面将有利于优化整机功耗。

(1) 处理器系统的低功耗管理;在处理及运算要求低的状态情况下,应注意适当降低处理器及存储器的运行时钟频率,这部分能够降低的功耗还是比较明显。

(2)液晶背光的管理;液晶模块的功耗主要是来自液晶的背光,这里一般采用直流LED背光方式,通过专用的LED背光驱动IC,可以调节LED背光的明暗强度,强背光和弱背光功耗差别较大。

(3)合理设计开机顺序。在硬件设计中,比如默认状态下,示波表的信号调理模块、高速ADC采集模块、液晶背光等均为节电控制状态,开机时,先启动处理系统模块,然后在逐步启动如液晶背光、模拟信号调理模块、数据采集系统等,这样可以有效降低开机时的冲击电流,达到保护电池和节电的目的。

5、结论

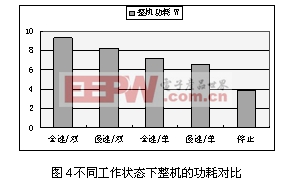

在手持示波表中采用多片相对低速的ADC交替采样,拼合实现高采样率的方法,不仅有利于实现低功耗动态管理,而且较低的数据流对于后端数据接收和存储是易于实现,另外采集系统的硬件成本也会大大降低。图4是对整机运行在不同工作状态时测试的功率消耗对比图,这里在不同状态下主要对ADC及模拟信号调理通道等进行了低功耗管理。

从图中看到,停止状态下的功耗不到全速双通道工作时消耗功耗的一半,由此可见,根据示波表各个工作状态,灵活控制各个模块的工作情况,达到功耗的合理分配,是非常有意义的,而多片ADC并行采样的方案为此提供了灵活的应用平台。

评论