基站调制解调器――为什么要现在选择多核?

根据功能分配任务

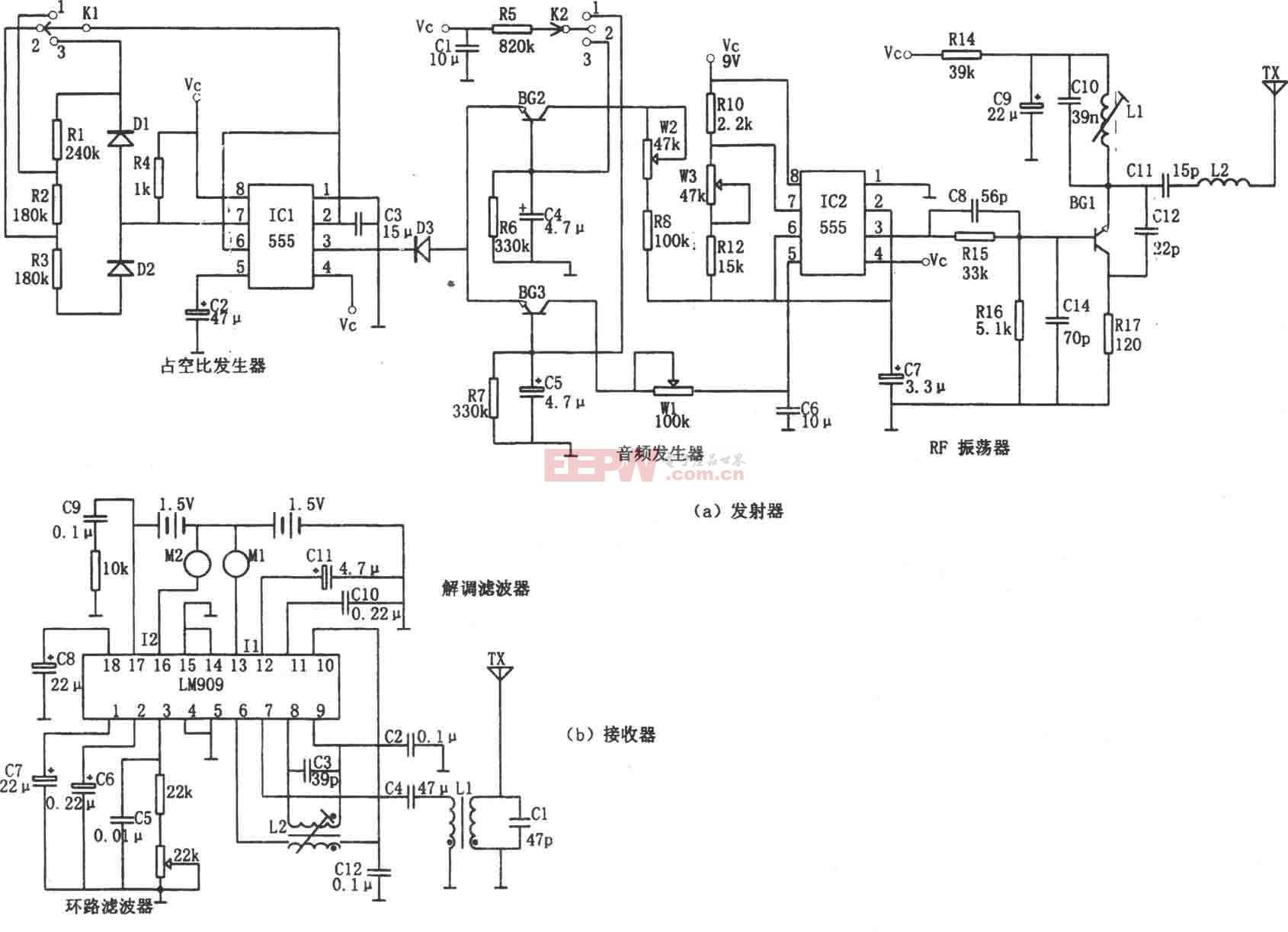

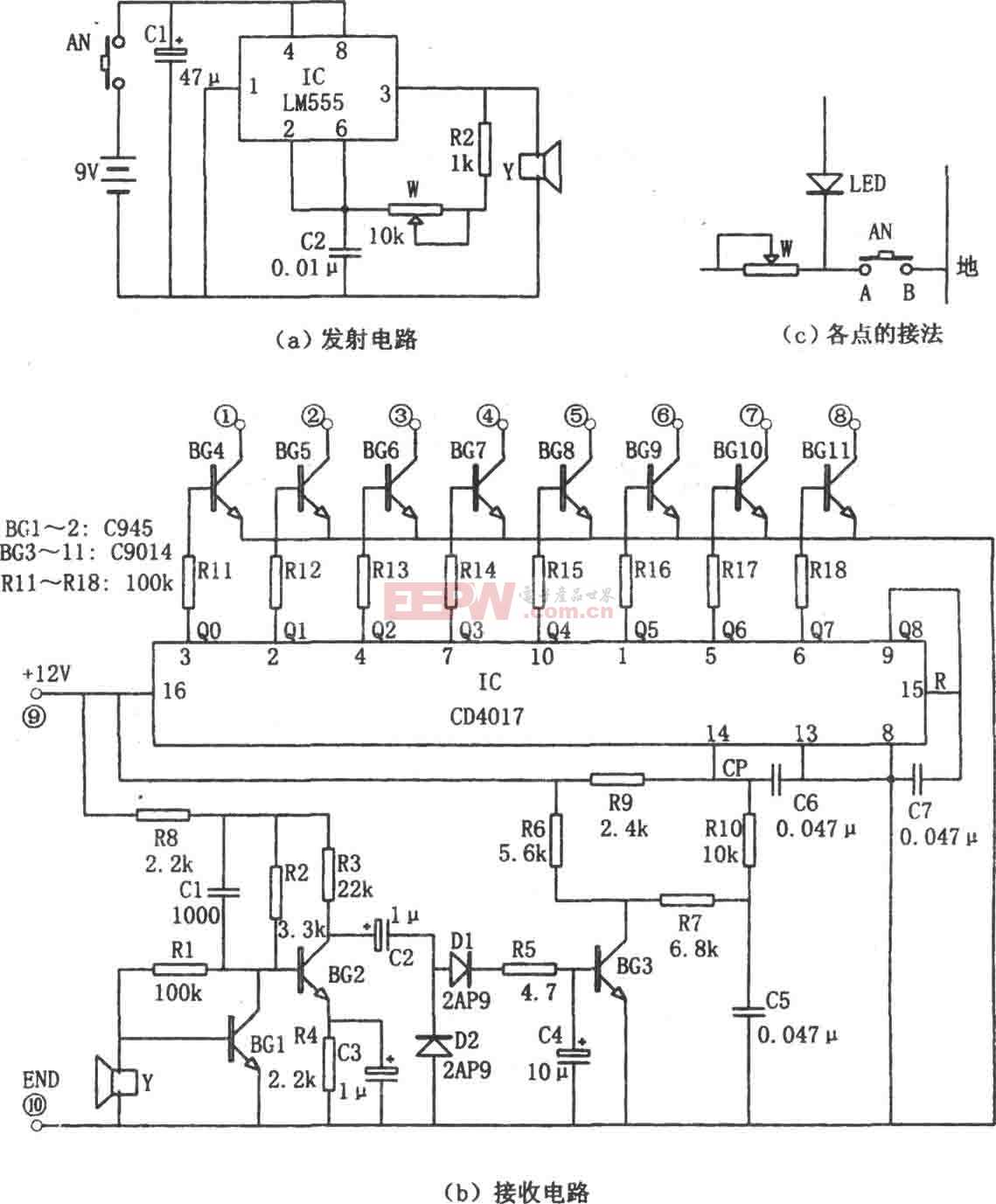

图 3 所示系统存在 7 项针对2 名用户按颜色划分的任务,其按功能分配。

图3:根据功能进行的任务分配。

在这种设计中,内核无需知道系统中存在多少用户。相反,它只需知道必须执行多少个唯一功能。随着用户数量增加,完成一项任务的时间也会随之增加。

如果在数据可用时立即调用某项任务,则会为每个用户调用每项任务,而且任务切换次数随用户数量增加而增加,这种情况会造成大量的任务切换次数。更好的方法是为每项任务分配一个链接列表。当任务完成时,将在该用户中执行作为该任务(与下项功能相关联)链接列表项目的系统。

这种方法不会随着用户在链接列表中的累加而产生中断。在每项任务被激活时,它会完成其链接列表或者运行至链接列表被抢占为止。其中一种选择是仅允许链接列表用户处理之间的抢占,这样用户功能就永远不会中断。这种选择可以在存储需求最低状态下实现抢占,因为所有需要的状态已经保存到相关列表中了。

其中一个关键的考虑事项是激活任务的频率:

• 简单的周期性中断:通过将任务分组到少量优先级队列可以进一步简化此类中断。在 WCDMA 中,只需两个队列即可获得良好的性能。其中存在单个周期中断,内核在切换到低优先级队列之前先清空高优先级队列。高优先级任务允许抢占时间更长的低优先级任务,而不需要随用户数增加的数据驱动中断。需要计算中断周期,以确保能够在最后期限之前以足够快的速度完成高优先级任务的最差情况负载。

• 多个周期中断:其能够迅速完成高优先级队列,同时在完成较低优先级队列之前保留尽可能多的时间。因此,只要不全部完成高优先级队列,就不会遗留低优先级队列中的任务。

• 队列达到特定大小时的中断:这是希望将中断次数最小化时执行队列的最有效方式,但是它会使任务的延迟取决于到达任务的数量。因此它不太适用于严格的实时系统。

• 队列头 (head of queue) 达到特定时限时的中断:可以实现一定时间内一定水平的服务保证,同时将中断次数最小化。为了实现上述目的可以为每个队列 头设置一个定时器,然后在定时器达到指定值时产生中断。如果需要处理队列头,则必须采取某种方法将定时器重新设置到下一个队列项目的等待时间长度。其适用于需要跟踪队列中各项任务所耗时间的复杂系统。

为了将任务数量和任务抢占开销保持在可控水平,它们不可根据用户数量而定。相反,任务应当与功能而不是与用户关联。由于目前的 BTS 为了实时满足客户需求而必须承担更多数据流量,因此这种设计越来越重要。

多核考虑

当今的 SoC 一般是多核 CPU ,采用独立的 IP 块,为了实现一个完整的调制解调器功能必须实现互操作和同步化。这种架构需要某种方式将优先级队列系统(图 4)映射至多 CPU 环境。

图4:基于功能的任务优先级队列。红色箭头表示处理顺序的依存性。

最简单的选项是将用户分配到相关 CPU,使每个 CPU 都保持其自己的队列。但是这样会有两个缺点:第一,所有用户有可能共享某些功能(如过滤与解调)。第二,某些功能可能需要共享协处理器或外设,造成它们不具有完全独立性。这样会造成一系列优先级队列之间的交互复杂化,从而难以保证实时性能。由于必须要支持多个 CPU 的存取,协处理器和外设也将变得更为复杂,因此必须决定 CPU 的哪项任务优先。所有这些都会增加软、硬件驱动程序的复杂性,使最终系统的测试更加困难、更加耗时。

为避免这些缺点,TI 采取了不同的方案:为单个 CPU 分配功能任务,从而使每个 CPU 都负责唯一一组功能。一般只加速特定类型功能的每一个协处理器都与单个 CPU 关联。这种方法可以显著简化协处理器所执行任务的排序。在许多情况下,外设也会与单个 CPU 通信,从而减少对不缺乏数据的任务进行检验所需的测试。

TI 的设计采用全系统同步排列 CPU 的帧、时隙 (slot) 与符号边界。这种通信采用由一项任务产生、发送到另一个任务的数据块来实现,一般由 L2 存储器之间的 DMA 执行。(每个 CPU 都具有其自己的 L2 存储器,因为共享存储器需要在速度等方面做出权衡折中。)

由于 TI DSP 可用于众多功能,因此 TCI6488 SoC具有高度的对称性。例如,所有 CPU 都可以访问接收机加速协处理器 (RAC)。这种设计允许在所有 CPU 上运行相同的功能并且允许所有 CPU 访问所有协处理器和外设资源。不过,TI 建议系统设计人员让一个 CPU 与 RAC 交互,以简化器件的操作。

通过实现 CPU的资源负载平衡,根据每项任务所采用的代码,一个 CPU 可能会先于其他 CPU 达到最高容量。解决方案是进行重新分组,但这需要软件架构改头换面 —— 这是在完成 CPU 测试时设计人员更愿意避免的情况。TI 相信,软件无线电方法与工具的进步会让软件分配变得更为轻松。

TI 采用代码周期估算、电子表格以及事务处理级模型来开发用于 WCDMA TCI6488 SoC 的建议软件分组。TI 相信,这种分组可以提供近乎完美的解决方案,同时仍然保留以下简单性:用一个 CPU 控制 RAC、一个 CPU 控制 TCP 和 VCP,以及用一个 CPU 执行 Tx 芯片频率加速和与天线阵列接口的输出通信。

对于其他标准(如不采用 RAC而是基于 OFDM 的标准),更易于开发对称软件架构。不过,即使在这些情况下仍然更便于分配此问题,这可以让一个 CPU 执行 FFT/IFFT 和部分调制/解调任务,而将相关结果发送至另一个 CPU 以便进行符号率处理。若用于天线数据,这种方法可以简化天线接口 或串行 RapidIO 与负责前端处理的 CPU 之间的通信。另外,其还可以简化后端符号率处理及其与以太网或串行 RapidIO 的通信。

评论