【E课堂】Σ-Δ型ADC拓扑结构基本原理

一阶Σ-Δ调制器的深入观察

本文引用地址://m.amcfsurvey.com/article/201609/310316.htmΣ-Δ调制器是一种负反馈系统,与闭环放大器相似。环路包含低分辨率ADC和DAC,以及一个环路滤波器。输出和反馈被粗略量化,常常只有一比特表示高电平或低电平的输出。ADC的模拟系统实现了这种基本结构,量化器就是完成采样的模块。如果存在保证环路稳定的条件,那么输出就是输入的粗略表示。数字滤波器获得该粗略输出并重构模拟输入的精确数字转换结果。

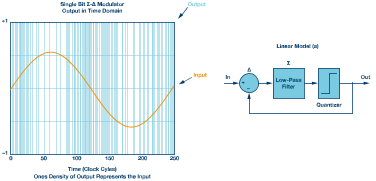

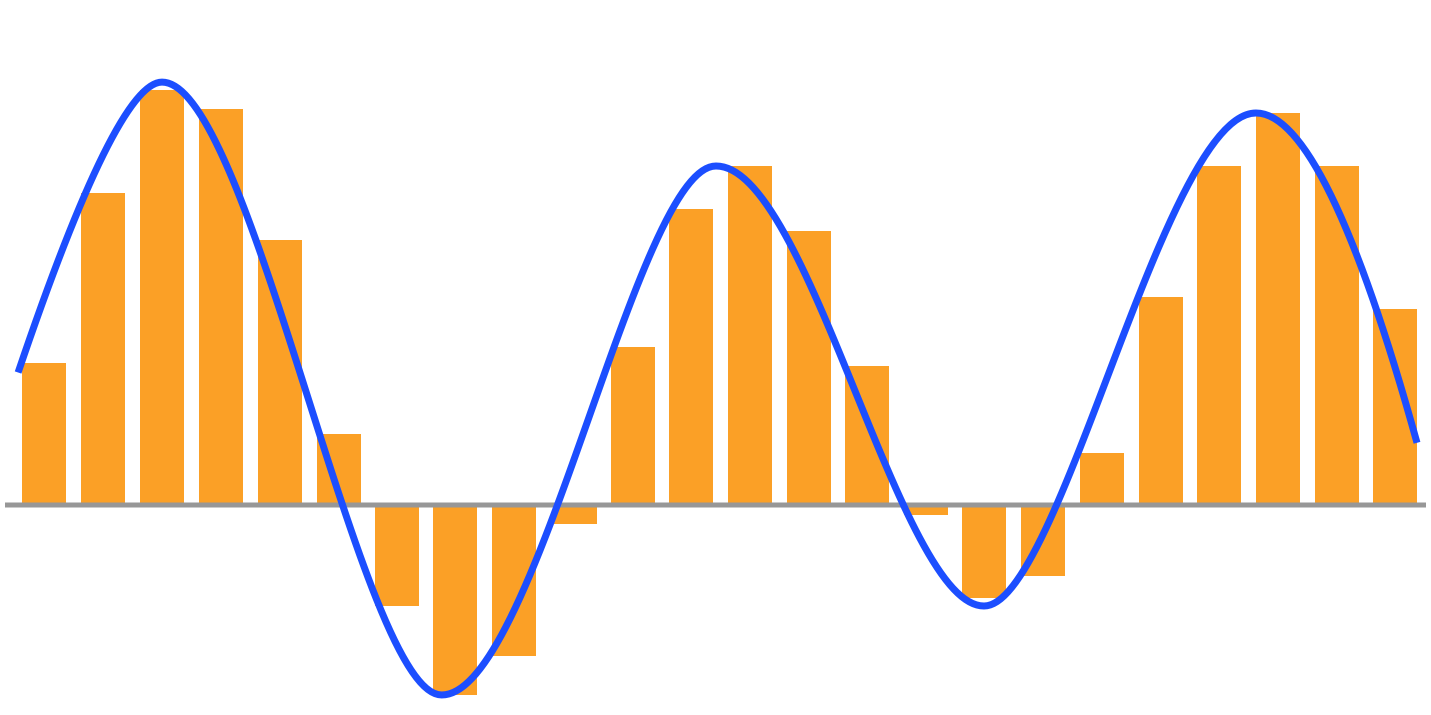

图4显示了响应一个正弦波输入的1密度输出。调制器输出从低电平到高电平的变化率取决于输入的变化率。当正弦波输入为正满量程时,调制器输出开关速率会降低,输出以+1状态为主。同样,当正弦波输入为负满量程时,+1和–1之间的转换会减少,输出以–1为主。当正弦波输入处于最大变化率时,调制器输出发生最高密度的+1和–1切换。输出变化率与输入变化率同步。因此,模拟输入由Σ-Δ调制器输出的转换率来描述。

若使用线性模型来描述这种1位调制器(Mod 1),则可将该系统表示为一个带负反馈的控制系统。量化噪声为量化器的输入与输出之差。输入偏差节点之后是一个低通滤波器。在图5b中,量化噪声用N来表示。

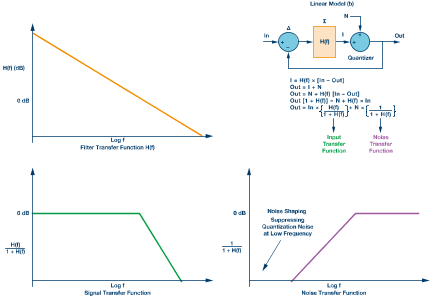

H(f)是环路滤波器的函数,定义噪声和信号的传递函数。H(f)是一个低通滤波器函数,在低频(目标带宽内)时具有非常高的增益,可衰减高频信号。环路滤波器可实现为简单的积分器或积分器级联。实践中常常把一个DAC放在反馈路径中,以便获取数字输出信号并将其转换为模拟信号反馈到模拟输入偏差节点。

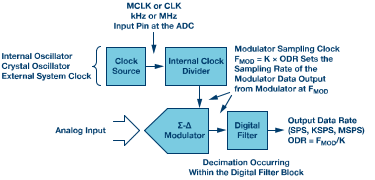

图3.Σ-ΔADC流程:从调制器输出到数字滤波输出的采样。

图4.输入正弦波的Σ-Δ输出1码值的密度。1阶Σ-Δ调制器环路的线性模型(a)

图5.Mod 1 Σ-Δ环路的线性模型(b),包括方程、滤波器、信号和噪声传递函数图。

解出图5所示方程便可得到信号和噪声传递函数。信号传递函数用作一个低通滤波器,在目标带宽内的增益为1。噪声传递函数是一个高通滤波器函数,提供噪声整形,在DC附近的较低频率,对量化噪声有很强的抑制。在超出目标带宽的较高频率看到的量化噪声会增加。对于一阶调制器(Mod 1),噪声以大约20 dB/十倍频程的速率提高。

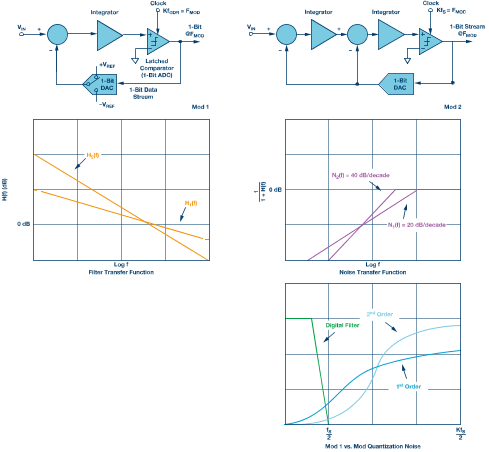

为了提高系统分辨率,常见方法是将两个环路滤波器级联起来以增加环路滤波器阶数。现在,总环路滤波器的H(f)具有更大的滚降,Mod 2型的噪声传递函数具有40 dB/十倍频程的上升速率。噪声所处的频率越低,噪声整形就越厉害。图6比较了Mod 1型和Mod 2型Σ-Δ ADC。Σ-Δ调制器的变化和样式非常多。规避了高阶1位环路稳定性问题的架构称为多级噪声整形调制器(MASH)架构。多级(MASH型)架构支持通过具有内在稳定性的低阶环路组合来设计稳定的高阶Σ-Δ调制器。

图6.Mod 1和Mod 2框图配置以及滤波器和噪声传递函数的比较图。

评论