S3C2440的时钟系统

3、Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。

MPLLCON的输入输出频率间的关系为

UPLLCON的输入输出频率间的关系为

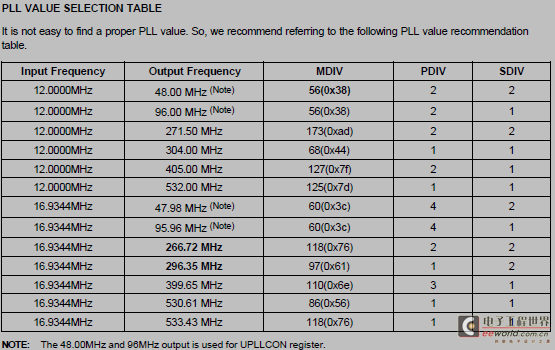

手工计算相对复杂些,我们可以根据欲得到的主频FCLK大小,直接通过查表来获知各倍频因子的设置参数。

对于12MHz的晶振,要想经过PLL电路得到405MHz,查表得应该设置MDIV、PDIV、SDIV分别为0x7f、2、1。

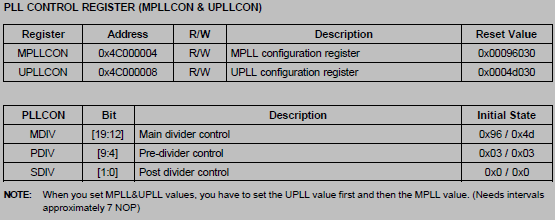

那在哪里设置MDIV、PDIV和SDIV这3个值呢,还是datasheet:

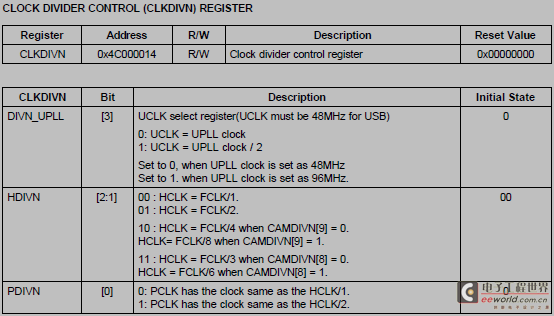

从上图可以看出,我们只需要设置MPLLCON寄存器就可以确定FCLK了,再通过CLKDIVN寄存器我们就可以设置FCLK、HCLK、PCLK三者之间的比例了。

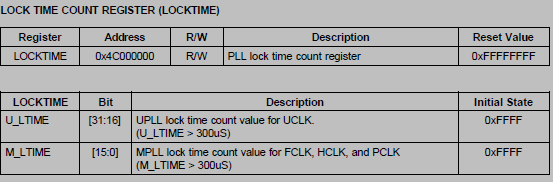

前面说过,MPLL启动后需要等待一段时间(Lock Time),使得其输出稳定。位[31:16]用于UPLL,位[15:0]用于MPLL。使用确省值0x00ffffff即可。

评论