面向纳电子时代的非易失性存储器

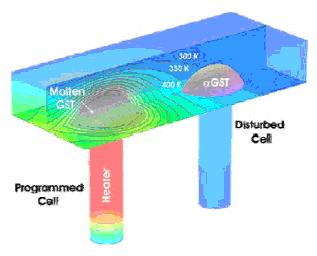

图3a - PCM原型结构的被写存储单元的自加热示意图

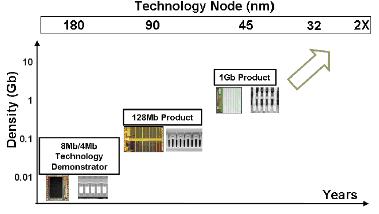

PCM的技术发展路线如图4所示。业界利用180nm技术节点开发出了首个芯片测试载具,并验证了此项技术的可行性。BJT选定的单元被高性能和高密度存储器选用,因为单元尺寸可以是"5F2 (其中F是存储单元半节距最小值)。虽然单元尺寸较大("20F2),但是集成存储器只需在逻辑制程中增加很少的掩模,成本优势十分突出,因此,MOS选定的单元适用于系统芯片或嵌入式应用。

图4 - PCM技术发展路线图

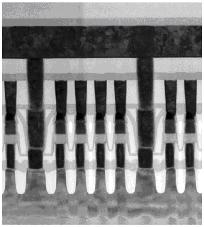

英特尔和意法半导体开发出一款叫做Alverstone的128Mb的90nm相变存储器,该产品现已实现商业化。另外一款 45nm 1Gb PCM产品现已进入高级研发阶段,该产品设计的单元尺寸为5.5F2 (图3-b)。

图3 b - 45nm技术PCM阵列的截面图

PCM技术研发将沿着不同的路线并行前进。主流的开发路线将是采用BJT选定的单元,沿着光刻技术发展路线,缩小现有技术架构,提供最小的单元尺寸。除广泛使用的 Ge2Sb2Te5以外,利用新的硫系合金是另外一个重要的研究领域,因为这可能会开创全新的应用领域;结晶速度极快或结晶温度更高的合金将会更有吸引力。

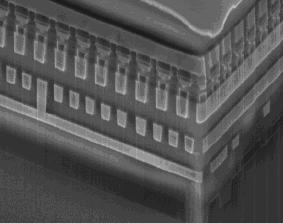

在存储器架构方面,一条研究主线将是利用真正的交叉点阵列,实现一层以上的存储器叠层。通过在后工序中集成p-n结或肖特基二极管作为选择元件,业界已经提出了不同的解决方法。硫系材料特别适合这种堆叠方法,因为在硫系材料堆叠后,其相变特性(像Ge2Sb2Te5)可以构成存储器元件,同时其电子开关特性(像OTS)构成选择元件(图5)。在这种情况下,单元尺寸可以达到4F2,位大小是单元尺寸的几分之一,具体大小取决于叠层数量,这项技术适用于高密度存储器,特别是存储应用。

图5 - 一层采用CMOS技术全集成的交叉点PCM阵列

总之,现有的技术成熟度,技术节点缩小能力,更广泛的应用范围,而且新材料和新架构可进一步扩大应用范围,这一切为相变存储器技术未来十年在存储器市场发挥重要作用铺平了道路。

评论