浅析数字电容隔离器的磁场抗扰度

电容隔离器的结构

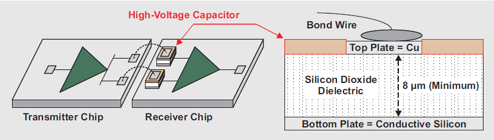

电容隔离器由两块硅芯片—一个发送器和一个接收机组成(请参见图2)。数据传输在由两个电容构成的差动隔离层之间进行,在每个电容的二氧化硅 (SiO2) 电介质两端都有一块铜顶片和一个导电硅底片。发送器芯片的驱动器输出通过一些接合线连接到接收机芯片上隔离电容的顶片。通过将电容的底片连接接收机输入构成了一个导电环路。图3显示了隔离层的等效电路结构图,并标示出了金接合线之间的环路区域。很明显,穿过该环路的磁场将会产生一个 EMF,其表示下面RC网络的输入电压噪声Vn1。我们常常碰到的第二种差动噪声部分Vn2,其产生原因是共模噪声到差动噪声的转换。两个噪声分量共同组成了综合噪声Vn。如果只考虑EMF的影响,则可以保守地将Vn一分为二:

图2 电容隔离器内部结构的简化结构图

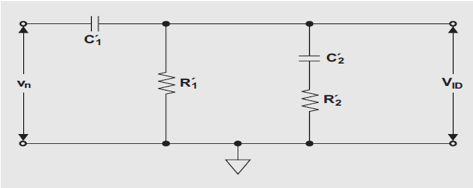

图3 隔离层的等效电路结构图

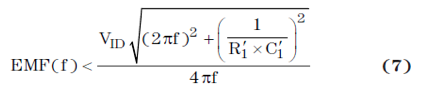

若要触发接收机,RC网络的输出必须提供一个差动输入电压VID,其超出了接收机输入阈值。是否出现伪触发,具体取决于RC网络的增益响应G(f)。

将差动网络转换为单端网络(请参见图4),简化了G (f) 的推导过程,但却要求C′1 = 2C1,R′1= R1/2,C′2 = 2C2,以及 R′2 = R2/2。

图4 单端RC网络

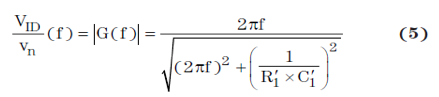

一次电路仿真证实了RC网络为一个一阶高通滤波器,其C′1和R′1为主要组件,频率高达100 MHz(参见图5中蓝色曲线)。超出这一频率以后,寄生组件C′2和R′2生效,从而引起稍稍偏离于线性的斜率。因此,频率达到100 MHz 以后,增益响应可以表示为VID/vn的比:

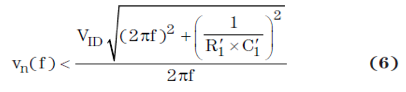

确定不会引起伪接收机触发的最大允许噪声,要求对方程式5求解vn:

然后,将vn代入方程式4,得到以伏特为单位的最大容许EMF:

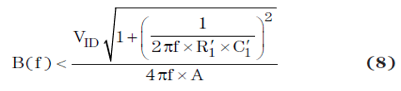

将EMF代入方程式3,得到最大可能磁通密度:

图5 增益幅度频率响应 |G(f)|

评论