示波器高级触发类型和控制(上)

窗口触发

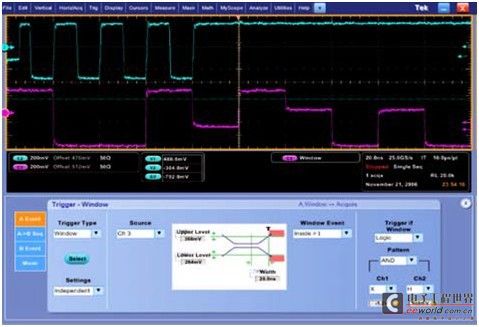

在许多高速设计中,多个内部元件总线在一块电路板上共享相同的总线。硬件或软件控制的缓冲阵列用来把正确数据复用到主总线上。复用器逻辑设计成在任一时间只允许一个单元使用总线。设计错误可能会导致总线争用,即在有两个逻辑电平的一条总线中会经历一种“中间”状态,在这种状态下,信号既不是‘1’也不是‘0’。窗口触发可以轻松捕获总线争用。通过窗口触发功能,示波器会触发进入(或退出)由两个用户可调节的门限定义的窗口的事件。此外,还可以使用窗口触发上的时间限定指标,构成一个矩形时间窗口,如果信号进入或退出这个窗口,那么会触发采集。最小窗口宽度是150 ps,最小重新准备时间为500 ps。图1g说明了捕获的总线争用事件。触发电平设置成相应逻辑家族的高和低门限电压。

图1g.窗口触发。

逻辑限定

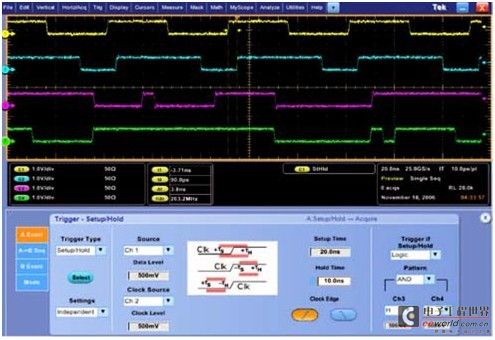

通过Pinpoint触发系统,还可以选择对上面所有高级触发类型(毛刺、宽度、欠幅脉冲、超时、跳变时间、建立时间和保持时间、窗口)进行逻辑判断,为隔离事件提供了另一个强大的工具。图2说明了使用逻辑限定捕获建立时间和保持时间,其中通道1 (黄色)和通道2 (蓝色)分别是时钟和数据。通道3 (洋红色)和通道4 (绿色)的触发事件都限定为逻辑高。只有在满足逻辑条件时,

才会在建立时间和保持时间违规时触发采集。在数字电路中,通常需要根据观察的信号的逻辑状态定义触发条件。4通道示波器可以使用最多四条输入的逻辑状态触发示波器。

图2.逻辑判定建立时间和保持时间触发

Pinpoint触发系统中有两种逻辑触发:

◆逻辑码型触发

◆逻辑状态触发

◆逻辑码型触发

逻辑触发(图3a)允许在提供的输入通道的任何逻辑组合上触发采集,特别适合检验数字逻辑操作。在输入通道满足逻辑码型(AND, OR, NAND, NOR)时,示波器会触

发采集。传统的逻辑家族(TTL 和ECL)提供了预先定义的门限电平,也可以使用USER 为逻辑家族设置门限,如高速CMOS。在MSO70000 系列上,可以把宽达20位的逻辑码型定义为触发条件。这特别适合隔离复杂设计中的特定系统状态,如定时检验至关重要的存储器总线。

图3a. 逻辑码型触发。

逻辑状态触发

与逻辑码型触发类似,在逻辑状态触发中,触发通过由通道4(及MSO70000 上的Clk/Qual)上的边沿提供时钟的通道1、2 和3(及MSO70000上的通道D0-D15)的任何逻辑码型定义,如图3b 所示。可以在时钟上升沿或下降沿上触发系统。在包含触发和位移寄存器的电路中调试传播时延和亚稳定问题时,这类触发非常有用。逻辑状态触发可以用来调试存在离散时钟线路和多个数据信号的并行总线;串行触发(后面将进行讨论) 则适用于触发串行总线中的嵌入式时钟数据。

图3b. 逻辑状态触发。

评论