FPGA最小系统之:最小系统电路分析

2.2.1FPGA管脚设计

FPGA的管脚主要包括:用户I/O(User I/O)、配置管脚、电源、时钟及特殊应用管脚等。其中有些管脚可有多种用途,所以在设计FPGA电路之前,需要认真的阅读相应FPGA的芯片手册。

下面以Altera公司的Cyclone系列FPGA为例,介绍FPGA的各种功能管脚。

(1)用户I/O。

I/Onum(LVDSnumn):可用作输入或输出,或者双向口,同时可作为LVDS差分对的负端。其中num表示管脚序号。

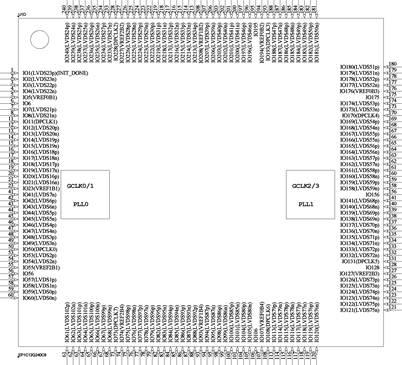

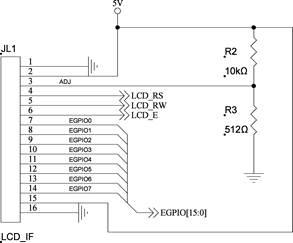

一般在绘制FPGA原理图时,将同一种功能和用途的管脚放在一个框图中,如图2.3所示是用户I/O的原理图。

(2)配置管脚。

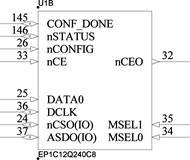

- MSEL[1..0]:用于选择配置模式。FPGA有多种配置模式,比如主动、被动、快速、正常、串行、并行等,可以此管脚进行选择。

- DATA0:FPGA串行数据输入,连接至配置器件的串行数据输出管脚。

- DCLK:FPGA串行时钟输出,为配置器件提供串行时钟。

- nCSO(I/O):FPGA片选信号输出,连接至配置器件的nCS管脚。

- ASDO(I/O):FPGA串行数据输出,连接至配置器件的ASDI管脚。

- nCEO:下载链器件使能输出。在一条下载链(Chain)中,当第一个器件配置完成后,此信号将使能下一个器件开始进行配置。下载链的最后一个器件的nCEO应悬空。

图2.3 FPGA用户I/O原理图

- nCE:下载链器件使能输入,连接至上一个器件的nCEO。下载链第一个器件的nCE接地。

- nCONFIG:用户模式配置起始信号。

- nSTATUS:配置状态信号。

- CONF_DONE:配置结束信号。

如图2.4所示是FPGA配置管脚原理图。

图2.4 FPGA配置管脚原理图

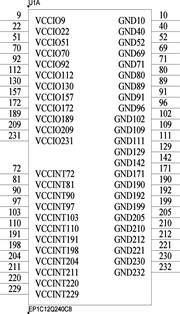

(3)电源管脚。

- VCCINT:内核电压。通常与FPGA芯片所采用的工艺有关,例如130nm工艺为1.5V,90nm工艺为1.2V。

- VCCIO:端口电压。一般为3.3V,还可以支持选择多种电压,如5V、1.8V、1.5V等。

- VREF:参考电压。

- GND:信号地。

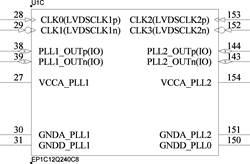

(4)时钟管脚。

- VCC_PLL:锁相环管脚电压,直接连VCCIO。

- VCCA_PLL:锁相环模拟电压,一般通过滤波器接到VCCINT上。

- GNDA_PLL:锁相环模拟地。

- GNDD_PLL:锁相环数字地。

- CLKnum(LVDSCLKnump):锁相环时钟输入。支持LVDS时钟输入,p接正端,num表示PLL序号。

- CLKnum(LVDSCLKnumn):锁相环时钟输入。支持LVDS时钟输入,n接负端,num表示PLL序号。

- PLLnum_OUTp(I/O):锁相环时钟输出。支持LVDS时钟输入,p接正端,num表示PLL序号。

- PLLnum_OUTn(I/O):锁相环时钟输出。支持LVDS时钟输入,n接负端,num表示PLL序号。

如图2.6所示是FPGA时钟管脚原理图。

图2.5 FPGA电源管脚原理图 图2.6 FPGA时钟管脚原理图

另外,FPGA的管脚中,有一些是全局时钟,这些管脚在FPGA中已经做好了时钟树。使用这些管脚作为关键时钟或信号的布线可以获得最佳性能。

(5)特殊管脚。

- VCCPD:用于选择驱动电压。

- VCCSEL:用于控制配置管脚和锁相环相关的输入缓冲电压。

- PORSEL:上电复位选项。

- NIOPULLUP:用于控制配置时所使用的用户I/O的内部上拉电阻是否工作。

- TEMPDIODEn/p:用于关联温度敏感二极管。

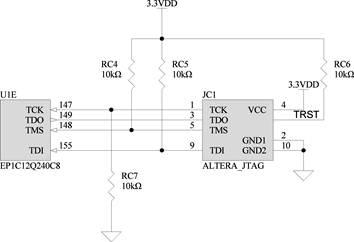

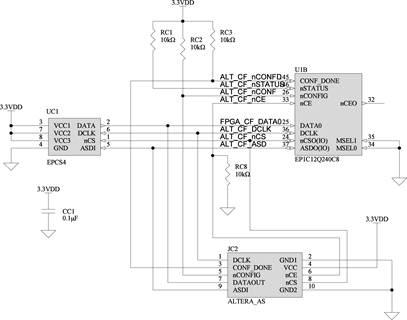

2.2.2 下载配置与调试接口电路设计

FPGA是SRAM型结构,本身并不能固化程序。因此FPGA需要一片Flash结构的配置芯片来存储逻辑配置信息,用于进行上电配置。

以Altera公司的FPGA为例,配置芯片分为串行(EPCSx系列)和并行(EPCx系列)两种。其中EPCx系列为老款配置芯片,体积较大,价格高。而EPCSx系列芯片与之相比,体积小、价格低。

另外,除了使用Altera公司的配置芯片,也可以使用Flash+CPLD的方式去配置FPGA。

在把程序固化到配置芯片之前,一般先使用JTAG模式去调试程序,也就是把程序下载到FPGA芯片上运行。虽然这种方式在断电以后程序会丢失,但是充分利用了FPGA的无限擦写性。

所以一般FPGA有两个下载接口:JTAG调试接口和AS(或PS)模式下载接口。所不同的是前者下载至FPGA,后者是编程配置芯片(如EPCSx),然后再配置FPGA。

如图2.7和图2.8所示分别是JTAG模式和AS模式的电路原理图。

图2.7 JTAG模式原理图

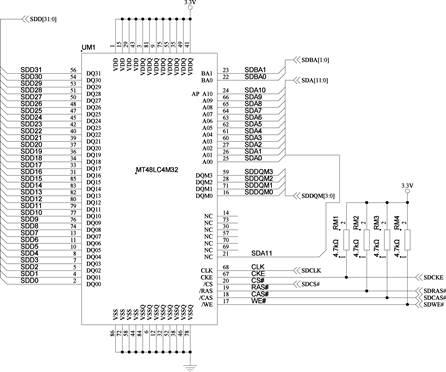

2.2.3 高速SDRAM存储器接口电路设计

SDRAM可作为软嵌入式系统的(NIOS II)的程序运行空间,或者作为大量数据的缓冲区。SDRAM是通用的存储设备,只要容量和数据位宽相同,不同公司生产的芯片都是兼容的。

一般比较常用的SDRAM包括现代HY57V系列、三星K4S系列和美光MT48LC系列。例如,4M×32位的SDRAM,现代公司的芯片型号为HY57V283220,三星公司的为K4S283232,美光公司的为MT48LC4M32。这几个型号的芯片可以相互替换。SDRAM典型电路如图2.9所示。

图2.8 AS模式原理图

图2.9 SDRAM典型电路

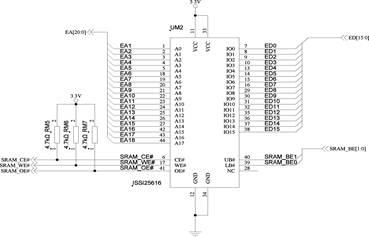

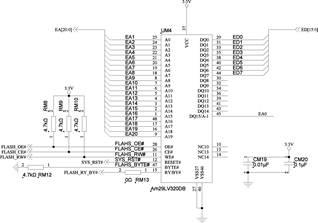

2.2.4 异步SRAM(ASRAM)存储器接口电路设计

由于ASRAM的读写时序相对比较简单,因此一般使用SRAM作为数据的缓冲,但其成本相对SDRAM高。而且作为异步设备,ASRAM对于时钟同步的要求也不高,可以在低速下运行。ASRAM主要为8位和16位数据宽度,用户可根据需要进行选择。ASRAM的典型电路如图2.10所示。

图2.10 ASRAM典型电路

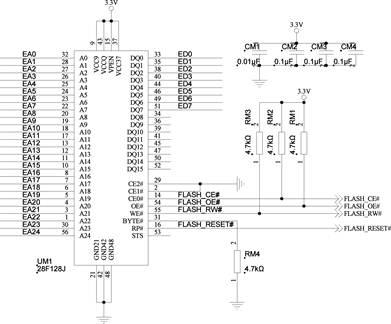

2.2.5Flash存储器接口电路设计

Flash可作为软嵌入式系统的程序存储空间,或者作为程序的固件空间。最常使用的是AMD公司或者Intel公司的Flash。在小容量的Flash选择上,AMD公司的Flash性价比较高,而高容量的Flash选择上,Intel公司的Flash性价比较高。

Flash同样也可以通过设置实现8位和16位的数据位宽,下面是几种典型的Flash应用。

16位模式下的(AMD)Flash连接如图2.11所示。

8位模式下的(AMD)Flash连接如图2.12所示。

8位模式下(Intel)Flash连接如图2.13所示。

图2.11 16位模式下(AMD)Flash连接

图2.12 8位模式下(AMD)Flash连接

图2.13 8位模式下(Intel)Flash连接

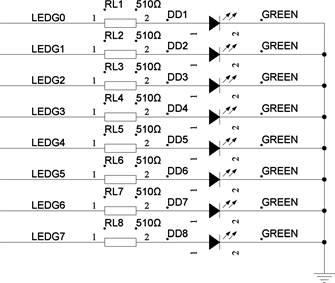

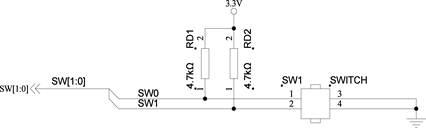

2.2.6 开关、按键与发光LED电路设计

发光LED参考电路如图2.14所示。

图2.14 数码管参考电路

拨码开关参考电路如图2.15所示。

图2.15 拨码开关参考电路

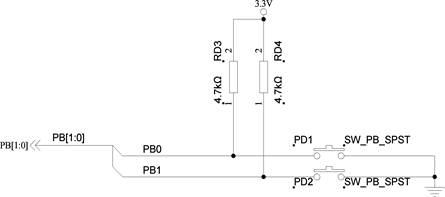

按键开关参考电路如图2.16所示。

图2.16 按键开关参考电路

2.2.7 VGA接口电路设计

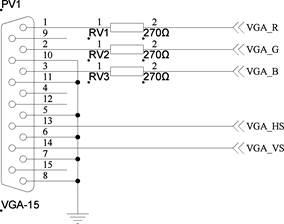

红色飓风开发板提供了VGA显示功能与接口,可以用普通的VGA电缆连接到计算机的显示器上。VGA 连接器定义如图2.17所示。

图2.17 VGA连接器定义

包括的信号有Red(R)、Green(G)、Blue(B)、Horizontal Sync(水平扫描HS)以及Vertical Sync(垂直扫描 VS)。系统结构示意图如图2.18所示。

图2.18 VGA接口结构示意图

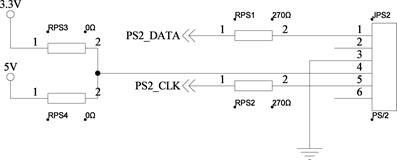

2.2.8 PS/2鼠标及键盘接口电路设计

早期的PS/2鼠标及键盘采用5V电压标准,目前的PS/2鼠标及键盘主要采用3.3V电压标准,如图2.19所示的参考电路可以实现对两种标准的兼容。

图2.19 PS/2参考电路

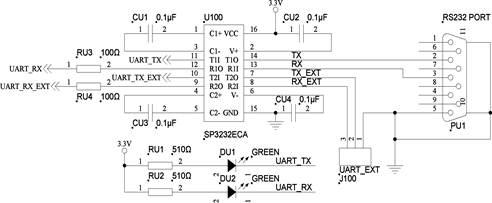

2.2.9 RS-232串口

RS-232接口定义如表2.1所示。

表2.1 RS-232接口定义表

25芯 |

9芯 |

信号方向来自 |

缩 写 |

描 述 |

2 |

3 |

PC |

TXD |

发送数据 |

3 |

2 |

调制解调器 |

RXD |

接收数据 |

4 |

7 |

PC |

RTS |

请求发送 |

5 |

8 |

调制解调器 |

CTS |

允许发送 |

6 |

6 |

调制解调器 |

DSR |

通信设备准备好 |

7 |

5 |

GND |

信号地 |

|

8 |

1 |

调制解调器 |

CD |

载波检测 |

20 |

4 |

PC |

DTR |

数据终端准备好 |

22 |

9 |

调制解调器 |

RI |

响铃指示器 |

DTE DCE设备信号电流方向如表2.2所示。

表2.2 DTE DCE设备信号电流方向表

9芯DTE |

25芯DTE |

电 流 方 向 |

缩写DCE |

描述DCE |

3 |

2 |

DTE→DCE |

2 |

3 |

2 |

3 |

DTE←DCE |

3 |

2 |

7 |

4 |

DTE→DCE |

4 |

7 |

8 |

5 |

DTE←DCE |

5 |

8 |

6 |

6 |

DTE←DCE |

6 |

6 |

5 |

7 |

DTE←DCE |

7 |

5 |

1 |

8 |

DTE←DCE |

8 |

1 |

4 |

20 |

DTE→DCE |

20 |

4 |

9 |

22 |

DTE←DCE |

22 |

9 |

RS-232参考电路如图2.20所示。

图2.20 RS-232参考电路

2.2.10 字符型液晶显示器接口电路设计

字符型液晶显示器电路原理图如图2.21所示。

第1脚:VSS为地电源。

第2脚:VDD接5V正电源。

第3脚:V0为液晶显示器对比度调整端,接正电源时对比度最弱,接地电源时对比度最高,对比度过高时会产生“鬼影”,使用时可以通过一个10kW的电位器调整对比度。

第4脚:RS为寄存器选择线,高电平时选择数据寄存器低电平时选择指令寄存器。

第5脚:RW为读写信号线,高电平时进行读操作,低电平时进行写操作。当RS和RW共同为低电平时可以写入指令或者显示地址,当RS为低电平、RW为高电平时可以读忙信号,当RS为高电平、RW为低电平时可以写入数据。

第6脚:E端为使能端,当E端由高电平跳变成低电平时,液晶模块执行命令。

第7~14脚:D0~D7为8位双向数据线。

图2.21 字符型液晶显示器电路原理图

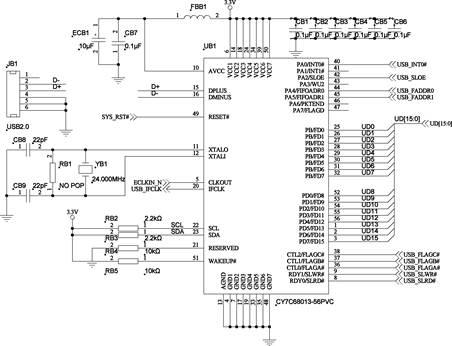

2.2.11 USB 2.0接口芯片CY7C68013电路设计

通过开发系统上的USB接口,可以用USB电缆直接将系统与主机(比如PC机)相连。USB接口使用了Cypress公司的CY7C68013芯片来实现,其电路原理图如图2.22所示。

图2.22 CY7C68013原理图

1.芯片介绍

Cypress Semiconductor公司的EZ-USB FX2是世界上第一款集成USB 2.0的微处理器。它集成了USB 2.0收发器、SIE(智能串行引擎)、增强的8051微控制器和可编程的外围接口。FX2这种独创性结构可使数据传输率达到56MB/s,即USB 2.0允许的最大带宽。

在FX2中,智能SIE可以硬件处理许多USB 1.1和USB 2.0协议,从而减少了开发时间和确保了USB的兼容性。GPIF(General Programmable Interface)和主/从端点FIFO(8位或16位数据总线)为ATA、UTOPIA、EPP、PCMCIA和DSP等提供了简单和无缝连接接口。

CY7C68013集成了以下特性。

(1)USB 2.0收发器、SIE(智能串行引擎)和增强性8051微处理器。

(2)软件运行。8051程序从内部RAM开始运行,可借助下列几种方式进行程序装载。

- 通过USB下载。

- 从EEPROM中装载。

- 通过外部存储器设备。

(3)4个可编程(BULK/INTERRUPT/ISOCHRONOUS)端点,可选双缓冲、三缓冲和四缓冲。

(4)8位或16位外部数据接口。

(5)通用可编程接口(GPIF)。

- 可以直接连接到并口,分为8位和16位。

- 可编程波形描述符和配置寄存器。

- 支持多个Ready输入和Control输出。

(6)集成标准8051内核,且具有下列增强特性。

- 可以达到48MHz时钟。

- 每条指令占4个时钟周期。

- 2个UARTS。

- 3个定时/计数器。

- 扩展的中断系统。

- 两个数据指针。

(7)采用3.3V电源系统。

(8)矢量USB中断。

(9)独立的数据缓冲区供SETUP和DATA包控制传输。

(10)集成I2C控制器,运行速度可达100kHz。

(11)4个FIFO,可与ASIC和DSP等无缝连接。

(12)专门的FIFO和GPIF自动矢量中断。

(13)可用于DSL Modems、ATA接口、相机、Home PNA、WLAN、MP3播放器、网络等。

2.USB启动方式和枚举

上电时,内部逻辑会检查连接到I2C总线上的EEPROM中的第一个字节(0xC0或0xC2)。如果是0xC0,就会使用EEPROM中的VID/PID/DID来替代内部存储值;如果是0xC2,内部逻辑就会把EEPROM中的内容装入到内部RAM中;如果没有检查到EEPROM,FX2就会使用内部存储的描述符来枚举。其缺省值是0x04B4/ 0x8613/ 0xxxyy。

当首次插入USB时,FX2会通过USB电缆自动枚举并下载固件和USB描述符表。然后FX2将再次枚举,通过下载的信息来定义设备。这两个步骤就叫做重枚举,当设备插入时它们就立即执行。

3.程序/数据存储器

(1)内部数据RAM。

FX2的内部数据RAM被分成3个不同的区域:低(LOW)128字节,高(Upper)128字节和特殊功能寄存器(SFR)空间。低128字节和高128字节是通用RAM,SFR包括FX2控制和状态寄存器。

(2)外部程序存储器和数据存储器。

FX2有8KB片上RAM(位于0x0000~0x1FFF范围内)和512字节Scratch RAM(位于0xE000~0xE1FF)。尽管Scratch RAM从物理上来说位于片内,但是通过固件可以把它作为外部RAM一样来寻址。FX2保留7.5KB(0xE200~0xFFFF)数据地址空间作为控制/状态寄存器和端点缓冲器。

注意 |

只有数据内存空间保留,而程序内存(0xE000~0xFFFF)并不保留。 |

4.端点缓冲区

FX2包含3个64字节端点缓冲区和4KB可配置成不同方式的缓冲,其中3个64字节的缓冲区为EP0、EP1IN和EP1OUT。

EP0作为控制端点用,它是一个双向端点,既可为IN也可为OUT。当需要控制传输数据时,FX2固件读写EP0缓冲区,但是8个SETUP字节数据不会出现在这64字节EP0端点缓冲区中。

EP1IN和EP1OUT使用独立的64字节缓冲区,可配置为BULK、INTERRUPT或ISOCHRONOUS传输方式,这两个端点和EP0一样只能被固件访问。这一点与大端点缓冲区EP2、EP4、EP6和EP8不同,这4个端点缓冲区主要用来和片上或片外进行高带宽数据传输而无需固件的参与。EP2、EP4、EP6和EP8是高带宽、大缓冲区,它们可被设置成不同的方式来适应带宽的需求。

5.外部FIFO接口

EP2、EP4、EP6和EP8大端点缓冲区主要用来进行高速(480Mbit/s)数据传输。可以通过FIFO数据接口与外部ASIC和DSP等处理器无缝连接来实现高速数据传输。它具有的通用接口有:Slave FIFO或GPIF(内部主)、同步或异步时钟、内部或外部时钟等。

6.中断资源

FX2的中断结构是在一个标准8051单片机的基础上增强和扩展了部分中断资源,中断资源如表2.3所示。

表2.3 FX中断资源表

FX2中断 |

中 断 来 源 |

中 断 向 量 |

优 先 级 |

IE0 |

INT0 Pin |

0x0003 |

1 |

TF0 |

Timer0 Overflow |

0x000B |

2 |

IE1 |

INT1 Pin |

0x0013 |

3 |

TF1 |

Timer1 Overflow |

0x001B |

4 |

RI_0 TI_0 |

USART0 Rx Tx |

0x0023 |

5 |

TF2 |

Timer2 Overflow |

0x002B |

6 |

Resume |

WAKEUP/WU2 Pin |

0x0033 |

0 |

RI_1 TI_1 |

USART1 Rx Tx |

0x003B |

7 |

USBINT |

USB |

0x0043 |

8 |

I2CINT |

I2C BUS |

0x004B |

9 |

IE4 |

GPIF/FIFOs/INT4 Pin |

0x0053 |

10 |

IE5 |

INT5 Pin |

0x005B |

11 |

IE6 |

INT6 Pin |

0x0063 |

12 |

其中27个USB请求共享USB中断,14个FIFO/GPIF源共享INT4。

芯片的详细介绍与使用方法可参看芯片数据手册。

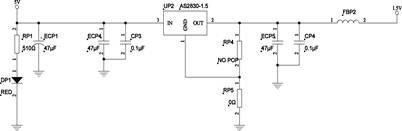

2.2.12 电源电路设计

电源是整个系统能够正常工作的基本保证,如果电源电路设计的不好,系统有可能不能工作,或者即使能工作但是散热条件不好,导致系统不稳定等异常情况。所以如何选用合适的电源芯片,以及如何合理地对电源进行布局布线,都是值得下大功夫研究的。

在选用电源之前要仔细阅读FPGA的芯片手册,一般来说FPGA用到的管脚和资源越多,那么所需要的电流就越大,当电路启动时FPGA的瞬间电流也比较大。通过数据手册中提供的电气参数,确定FPGA最大需要多大的电流才能工作。

下面是几种常使用的FPGA参考电源。

- AS117可以提供1A电流,线型电源(适用144管脚以下、5万逻辑门以下的FPGA)。

- AS2830(或LT1085/6)可以提供3A电流,线性电源(适用240管脚以下、30万逻辑门以下的FPGA)。

- TPS54350可以提供3A电流,开关电源(适用大封装大规模的高端FPGA)。

AS2830电源应用电路如图2.23所示。

对于线性电源芯片,输出电压和输入电压的关系为:Vout=(1+RP3/RP2)×Vref。

Vref一般是1.25V,输出假定输入Vin为5V,Vout为1.5V,那么RP2/RP3=1/5,而RP3一般要求100~150W,那么可以选RP3=100W,RP2=500W。如果采用了固定电平输出的芯片,只需要把RP3焊0W,RP2不焊接即可。

图2.23 AS2830电源应用电路

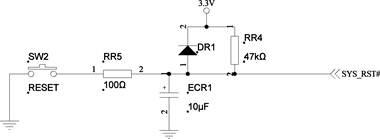

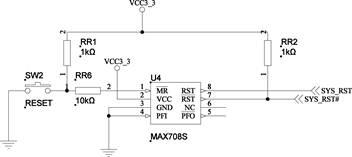

2.2.13 复位电路设计

一般复位电路采用的是低电平复位,只有个别单片机采用高电平复位方式。

常见的电平复位电路分为芯片复位和阻容复位。前者的复位信号比较稳定,而后者容易出现抖动。因此在成本允许的范围内我们一般推荐使用芯片复位。

常用的芯片复位有MAX708S/706S系列,它们可提供高、低电平两种复位方式和电源监控能力(监控电源电压低到一定程度自动复位)。

IMP811是一款比较低廉的复位芯片,只有低电平复位功能,但是其体积非常小。

阻容复位典型连接电路如图2.24所示。

图2.24 阻容复位典型连接电路

MAX708S典型连接电路如图2.25所示。

图2.25 MAX708S典型连接电路

IMP811典型连接电路如图2.26所示。

图2.26 IMP811典型连接电路

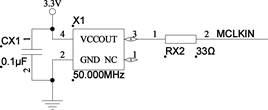

2.2.14 时钟电路设计

时钟电路典型连接如图2.27所示。

图2.27 时钟电路典型连接

评论