PCB叠层设计

1、问题点确认

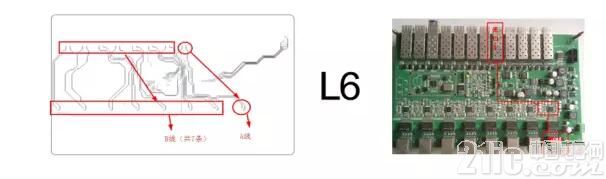

根据客户端提供的信息,确认为L6层光口8与芯片8之间的两条差分阻抗线调试不通;

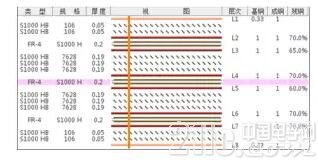

2、客户提供的叠构与设计要求

改善措施

影响阻抗信号因素分析:

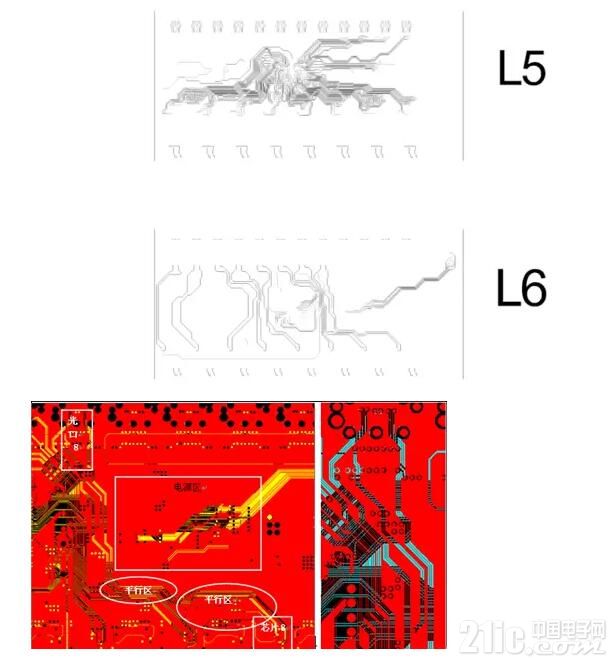

线路图分析:客户L56层阻抗设计较为特殊,L6层阻抗参考L5/L7层,L5层阻抗参考L4/L6层,其中L5/L6层互为参考层,中间未做地层屏蔽,光口8与芯片8之间线路较长,L6层与L5层间存在较长的平行信号线(约30%长度)容易造成相互干扰,从而影响了阻抗的精准度,阻抗线的设计屏蔽层不完整,也造成阻抗的不连续性,其他7组部分也有相似问题,但相对较轻微。

L56层存在特殊设计(均为信号层,存在差分阻抗平行设计、相邻阻抗层间未设计参考地层),客户端未充分考虑相邻层走线存在的干扰,导致调试不通问题。

与客户沟通对叠层进行优化,将L45、L56、L67层结构进行了调整,介质层厚度分别由20.87mil、6mil、13mil 调整为5.12mil、22.44mil、5.12mil,将而L4、L7间的参考地层间的距离拉近,L56层互为参考且屏蔽不足的线路层距离拉远,减少干扰。

优化后的叠层结构:

优化后的阻抗匹配:

改善效果

通过调整叠层结构,拉大L56层相邻信号层之间的距离,串扰造成的系统故障问题得到解决。

评论