EUV技术开启DRAM市场新赛程

SK海力士公司在7月12日表示,本月已经开始生产10纳米8Gb LPDDR4移动DRAM—— 他们将在该内存芯片生产中应用极紫外(EUV)工艺,这是SK海力士首次在其DRAM生产中应用EUV。

本文引用地址://m.amcfsurvey.com/article/202107/427051.htm根据SK海力士的说法,比起前一代规格的产品,第四代在一片晶圆上产出的DRAM数量增加了约25%,成本竞争力很高。新的芯片将在今年下半年开始供应给智能手机制造商,并且还将在2022年初开始生产的DDR5芯片中应用10纳米EUV。

世界第三大DRAM制造商SK海力士发布声明,正式启用EUV光刻机闪存内存芯片,批量生产采用新一代10纳米级第4代(1a)微细工艺的8Gbit(千兆位)LPDDR4。这则简短资讯在半导体圈子中引发热议,这预示着国际之间,新一轮半导体尖端技术的革新竞争正式开始。

DRAM制造进入EUV新时代

从原理层面上看,一个最简单的、存储一个Bit信息的DRAM Storage Cell的结构主要是由存储电容(Storage Capacitor)、访问晶体管(Access Transistor)、字线(Wordline)以及位线(Bitline)四部分组成。

其中,存储电容通过存储在其中的电荷的多和少,或者说电容两端电压差的高和低来表示逻辑上的1和0;访问晶体管的导通和截止决定了允许或禁止对存储所存储的信息的读取和改写;字线决定了访问晶体管的导通或者截止;位线则是外界访问存储电容的唯一通道。

对于一种这样设计的器件,如何缩小其工艺尺寸,就成为了降低DRAM成本和尺寸的关键。

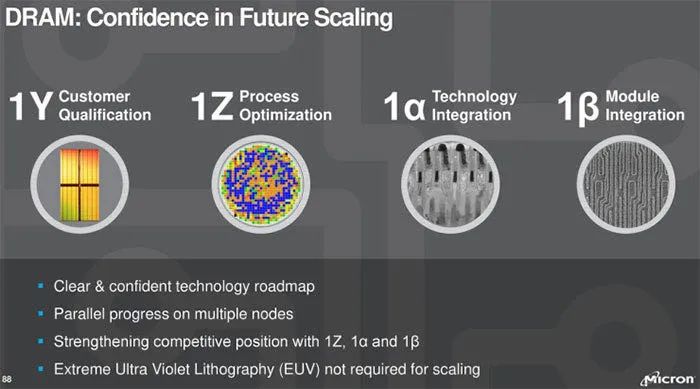

回顾DRAM过去多年的发展,在历经了2008年的40nm级别、2010年的30nm级别的推进后,自2016年以来就一直在10nm级别(19nm到10nm或1X)徘徊,三大存储厂商(三星、SK海力士和美光)也都推出了多代的工艺。当中的每一次升级,都涉及在某些维度上减小DRAM单元尺寸,以实现增加密度和降低功耗的目的。

了解DRAM演进历史的人都知道,工艺的竞争是永恒的旋律。随着产品的技术更新,半导体行业开始将代表着技术革新工艺节点的每一代产品用标注英文字母的方式命名。在进入20nm节点以后,通过三代工艺去制造DRAM,这就是1Xnm,1Ynm和1Znm。而这次SK量产的1anm DRAM则是第四代产品。

SK海力士对10纳米级第四代DRAM实现量产对整个世界半导体市场都有着重要意义,它标志着采用EUV设备进行高精度DRAM的批量生产成为可能。

三大厂商先后出招

统计数据显示,目前全球DRAM的市场份额主要控制在三星、SK海力士和美光手中。参考2020年Q3的市场份额占比,三星占据41.3%,SK海力士占28.2%,美光占25%。三家合计占了全行业近95%的市场份额。

在看到了EUV的机会后,三星、SK海力士和美光这三大DRAM大厂已经先后进入了EUV DRAM市场,或者至少已经公布了公司的EUV DRAM规划。其中,三星是当中的先头兵。

在DRAM领域,三星是最先宣布EUV DRAM进展的公司。得益于半导体制造领域的技术优势,早在去年3月份,三星便对外宣布基于EUV的第一代10nm DRAM(D1x)已完成其客户评估,首批交付的模块达到了100万块量级。

仅仅过去半年之后,三星再次放出消息称,其位于韩国平泽的第二条生产线已开始量产业界首款采用EUV技术的16Gb LPDDR5,带宽高达6400Mbps。三星估计,使用EUV工艺生产DDR5内存,其12英寸D1a晶圆的生产效率会比旧有的D1x工艺的生产力提升一倍。

三星总结了采用EUV技术生产DRAM的好处 —— 首先,可以用更小、更精细的形式绘制电路;其次,大幅节省了掩模成本和光刻处理步骤;第三,在相同的表面积中能够存储更多的数据;此外,芯片能耗更令人满意。

如今,SK海力士已经成为全球第二家采用EUV光刻技术量产LPDDR产品的公司。SK海力士表示,在此前生产1y纳米级产品过程中曾部分采用了EUV技术,事先完成了对其稳定性的验证,此次量产确保了EUV工艺技术的稳定性,未来1a纳米级DRAM都将采用EUV工艺进行生产。

相比之下,美光显得比较谨慎。10纳米级DRAM是今年1月,由美光首次出货的,这给市场带来了不小的震动。不过,美光将使用现有的氟化氩(ArF)工艺而不是EUV来生产该产品。与EUV工艺相比,现有的Arf工艺对于器件的高效率、以及超小型化会产生不利的影响。

不过,过去多年稍显保守的美光也宣布,将在2024年生产基于EUV的DRAM。至此,三大DRAM大厂都跨入了EUV时代。

半导体行业正在准备迎接新的飞跃,全球DRAM市场领头羊三星电子和SK海力士即将开启“EUV DRAM”时代。

随着制程工艺的提升,节点的进一步微缩,EUV的性能和成本正在不断优化,DRAM将迎来EUV时代只是早晚的问题。

以EUV的引入来实现技术上的领先,对存储器厂商来说也是无可厚非。考虑到DRAM产品的同质性,通过引入更高制程来获得性能差异,从而获得市占率,是一条已经验证过无数次的绝招。

三星电子和海力士正寻求通过自己的EUV DRAM技术实现差异化,这可能会导致市场的寡头垄断结构发生变化,而这种情况本不可能改变。EUV DRAM将进一步扩大韩国半导体企业与中国半导体企业之间的差距。

只是这样将促使行业竞争更趋白热化,后进者如中国国内的DRAM厂商,如果要有所突破,势必面临更大的压力。

不过光刻机厂商ASML估计,在DRAM芯片制造方面,每月每启动100,000个晶圆制造项目,一层就需要1.5到2个EUV系统。因此,DRAM制造商需要考虑根据容量和产能来规划相关设备。

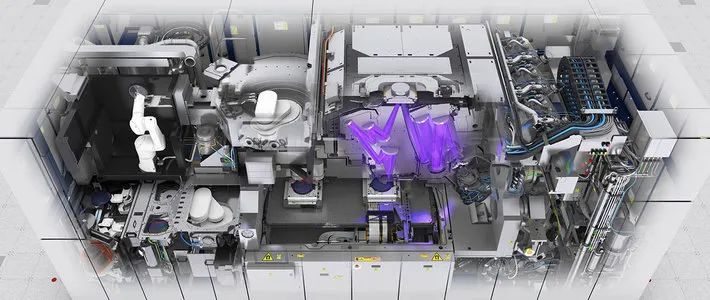

EUV光刻机技术

为什么是EUV?所谓EUV,也就是Extreme ultraviolet lithography的简称。EUV光刻机技术是指在极紫外光下,通过反射投影光学系统,将反射掩模上的图形投影成像在硅片表面的光刻胶上。这种技术的精细度极高,可以减少多种图形制作中的重复步骤,提高图形分辨率。

因为近几年的科技竞争,大家对这个使用在荷兰光刻机大厂ASML新型光刻机的技术并不陌生。得益于其波长特性以及先进的设计,EUV光刻机近年来被广泛应用到先进工艺逻辑芯片的生产中。

但其实根据ASML在2018年的规划,这也是一种会被存储领域采用的新技术。

SK海力士方面表示,多年来,半导体光刻设备取得了许多进步,采用具有高数值孔径 (NA) 的大透镜或使用短波长光作为光源。然而,随着栅极长度减小到30nm以下,现有沉浸式ArF光刻设备的图案化能力达到了极限。

按照SK海力士的说法,半导体行业一直在准备以EUV光刻机实现10纳米级规模的工艺。通过利用13.5nm波长的光,EUV光刻机较之现有的193nm的ArF实现更精细的半导体电路图案,而无需进行多重图案化。借助这种方式,能将处理步骤的数量减少了,因此制造时间比当前的多重图案化技术(如四重图案化技术(QPT))更短,从而使EUV成为迄今为止唯一的突破。

三星方面也表示,EUV能够帮助绘制更精细的电路,因此可以让芯片在相同的表面积内存储更多的数据。同时,使电路更精细意味着更多的逻辑门能够安装在单个芯片中。通过这样的方式,就可以让芯片变得更强大,更节能。在部署EUV后,芯片的表面积得到了更有效的利用,为此业内的人争先恐后地为自己的生产线完善这项技术。

另外,EUV技术在DRAM中的应用让增加传输速率的同时减少了20%的功耗,这将减少二氧化碳的排放,有利于践行绿色发展观。

然而,EUV设备和所需的基础设施是昂贵的。此外,芯片公司在首次采用该技术时可能面临产量问题。

虽然EUV能够给DRAM供应商带来不少好处,但为DRAM实施EUV面临以下几个挑战:局部临界尺寸均匀性(Local Critical Dimension Uniformity:LCDU),因为这种变化会改变电气性能和蚀刻纵横比;孔尺寸– EUV对孔尺寸敏感,并且加工窗口狭窄;薄抗蚀剂– EUV抗蚀剂非常薄,需要硬化。

EUV的一个主要问题是狭窄的工艺窗口;此外,当今的电容器间距极限大于40nm,这也是当前电容器图案化的EUV极限。将来将需要更小的间距,并且工艺可变性需要提高30%以上,才能实现缩放。

EUV不足够解决DRAM的微缩问题,这可能需要在3至5年后,引入一种新的DRAM架构。当中涉及的一个有趣的选择是3D化,那就是将电容器从垂直结构变为堆叠的水平结构。

当前世界经济正处于后复苏时期,各个半导体厂商都不敢轻易扩大自身产能,而是致力于制程技术优化来增加对市场的供应能力,利用EUV光刻机进行先进芯片的生产也被看作未来半导体市场的发展方向。

与三星、SK海力士等DRAM巨头厂商相比,我国DRAM产业还处在发展阶段,产业链相对薄弱。SK海力士对运用EUV光刻机技术进行1anm DRAM量产的实现,将拉开与其它厂商间的差距,抢占更多的市场份额,这会给我国的DRAM市场带来强烈的冲击。

评论