降低时间成本提升良率 泰瑞达为半导体测试提速

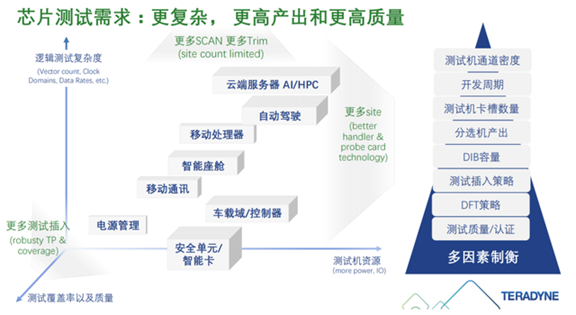

芯片测试贯穿于半导体研发到量产的全部过程,是半导体制造无法绕开的一环。虽然近些年半导体工艺的演进速度放缓,但因为制造工艺的精细和芯片内部结构的复杂,使得测试和验证的复杂程度大幅提升。

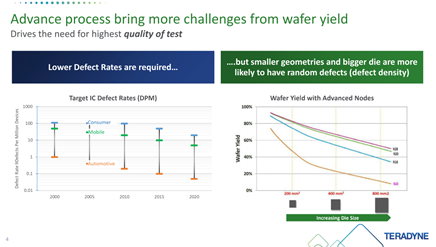

新工艺,新挑战

随着制作工艺越来越先进,芯片上的晶体管集成度也越来越高。为数量暴增的晶体管进行测试势必会造成芯片测试时间的增加。另外,模拟和射频芯片测试过程中模拟测试占比重较大,且在测试之前需在内部进行trim调整,这样会带来额外的测试时间,测试时间的增加,就意味着更高的测试成本。Wafer yield也是先进工艺带来的一个挑战,wafer的初次yield不断下降。越来越复杂的芯片也让每颗芯片的Die size不断增加,进而增加芯片的失效概率。

泰瑞达的应对之道

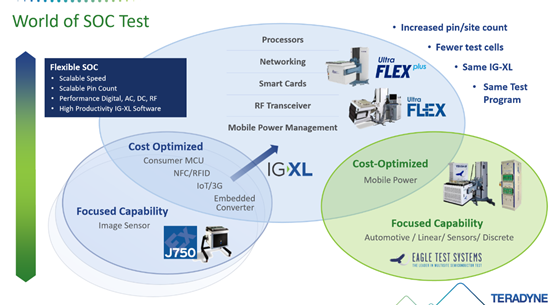

作为ATE领域的领军企业之一,泰瑞达(TERADYNE)拥有雄厚的技术积累和完整的半导体测试解决方案。过去多年中,泰瑞达已经推出了多款测试设备,包括测试低成本解决方案J750和用来应对更高级别测试需求的UltraFLEX系列。

泰瑞达销售副总经理黄飞鸿介绍表示:“日新月异的终端市场在拉动芯片需求大幅增长的同时,也对测试平台有了更严格的要求。”为了应对“量产数据激增”、“量产测试时间大幅延长“等诸多新型挑战。泰瑞达旗下产品UltraFLEXplus高性能SoC测试平台应运而生,并利用UltraFLEX过去 15 年累积开发的测试 IP,使产能和工程效率的得到了跨越式的改善。

泰瑞达的测试解决方案及适用范围示意

多维度升级,满足新兴测试需求

UltraFLEXplus平台对芯片测试接口板设计进行了完全革命性的改进,采用Broadside技术可使接口板的应用区域扩大,同时降低接口板PCB层数。通过简化原本复杂的 DIB布局,实现更快的上市时间、和更高的PCB良率。

UltraFLEXplus系列还增加了工位数,并通过提高并行测试效率来减少多工位测试时间开销,从而满足测试需求。减少测试单元的数量可以最大程度降低总制造成本。除此之外UltraFLEXplus引入了创新性的PACE运行架构,实现板卡控制下放,提升处理效率,以最小的工程量创造出最高的测试单元产能。可助力工程师更快、更好地完成更繁重的测试任务。

黄飞鸿表示:“值得一提的是,J750、UltraFLEX以及UltraFLEXplus三款产品均使用统一的测试软件平台IG-XL,这就意味着工程师开发的程序可以轻易在上述设备间实现无缝迁移,这无疑将简化开发难度、缩短开发时间,测试工程师能够以更少的工作量将更高质量的新测试程序发布到量产环境中。”

IG-XL软件、独有的 PACE 架构和 Broadside 应用接口的完美结合,使得新一代测试平台UltraFLEXplus无论是测试效率,测量精准度,各方面指标都有极大的提升。

目前,UltraFLEX测试平台全球装机量已经达到5000套,而IG-XL软件平台装机也超过了12000套。泰瑞达具备丰富的市场验证经验,在UltraFLEXplus新平台发布一年半以来,全球装机量已接近600套,并以其优异的表现得到了市场的青睐与客户的认可。

评论