一种应用于折叠/插值型ADC的高速宽带采样保持电路

近20 年来,随着数字通信的快速发展,处于信号链路中的模数转换器(ADC)的作用就越来越重要。其中超高速宽带ADC 可广泛应用于卫星、雷达、电子战、数字示波器、通信等接收机领域[1,2]。传统高速8位ADC 一般采用全并行结构,尽管该结构转换速度快,但电路规模随分辨率n 呈2n 指数增长[3,4],且功耗大。折叠/ 插值型结构ADC 利用折叠与插值转换关系,可大大减少并行比较器数量,同时转换速率与全并行结构相当。但是,即使采用双极工艺,折叠结构电路依然受器件失配影响很大,幸运的是可以采用前端数字校准算法来降低器件失配对电路性能的影响。

本文引用地址://m.amcfsurvey.com/article/202205/434595.htm折叠/ 插值型ADC 的器件失配可以用前端数字校准算法进行修正,但要校准动态的时钟抖动误差则需付出极大代价。因此,折叠/ 插值型ADC 的前端一般采用高速宽带采样保持电路(S/H),可以有效降低采样时钟抖动影响。本文提出的一种基于0.18 μm BiCMOS工艺设计的开环采样保持电路,采用简易的数字校准算法即可大大降低电路的增益误差与失调误差。电路仿真与实际测试表明,通过数字校准采样保持电路增益与失调误差后,ADC 的动态性能可提升10 dB 以上。

1 采样保持电路设计

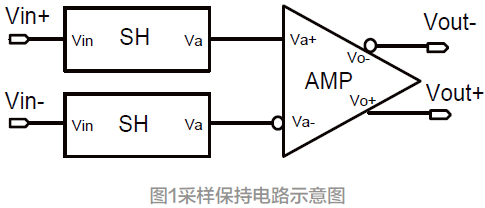

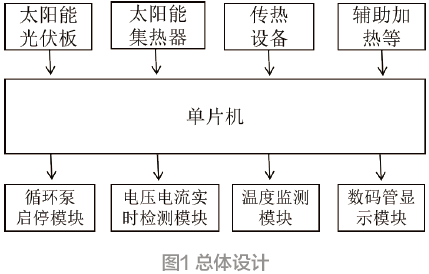

采样保持电路的采样率达到2GSPS,所以S/H 电路采用开环结构。如图1 所示,S/H 电路系统由采样保持级(SH)电路和放大与驱动级(AMP)电路组成。

在SH 级,电路采用伪差分结构,然后在AMP 级中转换成差分信号来提高抗干扰能力。模拟输入信号Vin 被采集并保持,由于SH 级电路采用开环结构以及电路带宽影响,SH 级电路的放大倍数小于“1”。AMP级电路对SH 级输出的保持信号进行放大,使S/H 电路系统的信号放大倍数刚好为“1”。此外,AMP 级电路不仅具有强大的驱动后级较大规模折叠电路的能力,还起到消除后级电路对采样保持转换时带来的馈通效应,提升S/H 电路采样转换时的线性度。

2 SH级电路设计

为了消除SH 级电路输入对管电流随输入信号变化带来的影响,本设计中输入管采用PMOS管代替双极管。SH 级电路如图2 所示。由于电路的采样率高达2GSPS,所以采用开环结构,尽可能提高电路转换速度。在SH级输出端加入一个几十欧姆小电阻,用来调整采样/ 保持转换过程中建立信号的过冲效应,以便获得最快转换速度。SH 级电路的带宽BW如式(1)所示。

式(1)中,RL是SH级电路输出端电阻,CL是SH级电路输出端电容。为了保证模拟输入频率高达2.5 GHz时,电路的无杂散动态范围(SFDR)超过65 dB,则保持电容值必须小于0.8 pF。采用小保持电容值可以提升采样保持电路带宽,同时会降低采样相时SH 级电路的线性度。但是,保持相时要提升电路线性度则需要加大采样保持电容值。此外,增加保持电容值可以减小采样转换时对保持电压的干扰。综合考虑[5],采样保持电容值选择0.5 pF。

3 AMP级电路设计

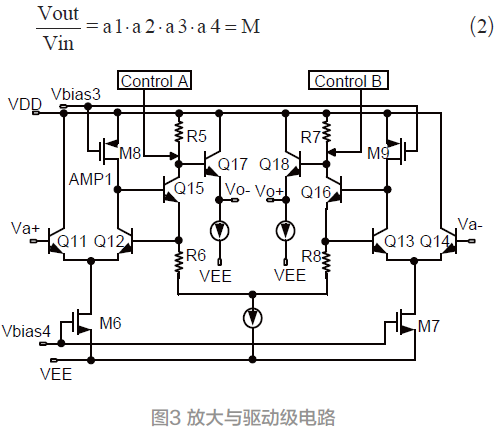

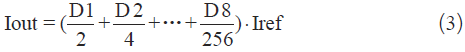

放大驱动级电路的作用是把SH 级输出的伪差分信号变化真正的差分信号,并驱动后级折叠转换电路。AMP 级采用一个简单的开环放大器,如图3 所示。SH级电路的增益为a1;放大器单元由Q11,Q12,M6 andM8 组成,其增益为a2;用于调整增益的电阻R5 与R6之间比值(R5/R6)为a3;输出管Q17 与Q18 的增益为a4。那么整个采样保持电路的增益如式(2)表达:

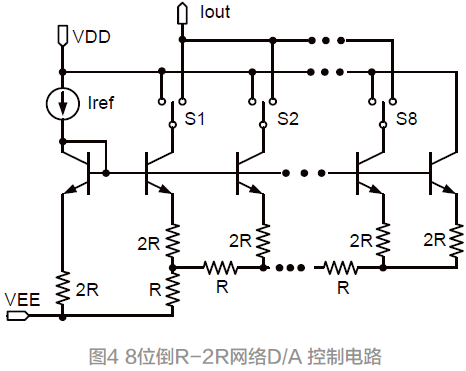

在a1,a2,a4 随工艺及环境偏差而变化的情况下,可以通过调节R5/R6 的比值,使采样保持电路的增益刚好为1。在Q17 与Q18 的基极处加入数字控制电路control A 与control B(control A 与control B 相同),分别调节流过电阻R5 与R7 的电流。数字控制电路如图4 所表,采用8 位倒R-2R 网络D/A 结构。采样保持电路输出电压由R5⋅ Iout (R7 = R5) 进行调节失调电压。当采样保持电路的增益小于“1”时,同时调节controlA 与control B,并使流过电阻R5 与R7 的电流减小,直到整个ADC 系统刚好达到满度为止,此调节动作都是在系统自校正过程中完成;反之亦然。

在图4 中,最大权重数字码D1 控制开关S1。如果D1 为“1”,S1 右开关导通;如果D1 为“0”,S1 左开关导通。同样地,D2 控制S2,D3 控制S3……D8 控制S8。通过DAC网络控制流过R5的电流表达式如式(3)所示:

4 版图设计与电路测试

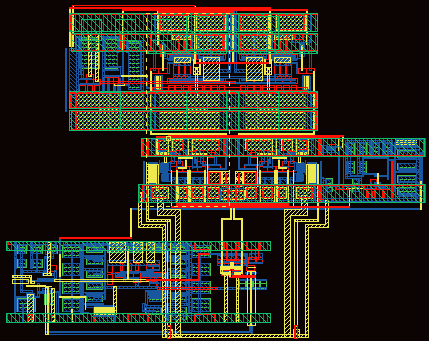

设计的采样保持电路的版图如图5 所示。

图5 S/H电路版图

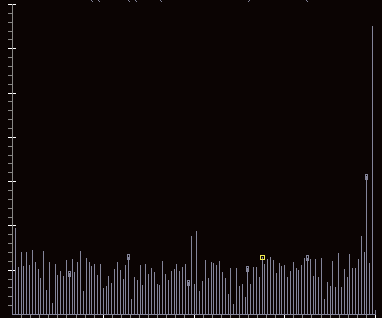

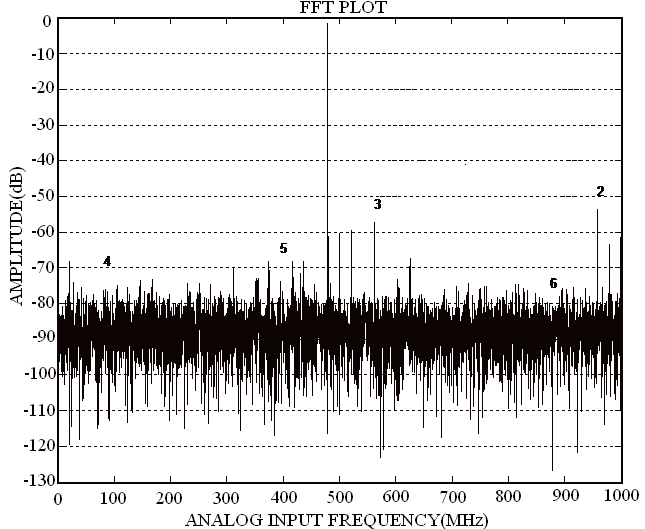

在模拟信号输入频率992 MHz、输入幅度500 mVpp,采样率2GSPS 条件下对版图进行后仿真,后仿结果如图6 所示,SFDR 为65 dB,满足ADC 设计要求。

图6 S/H电路版图后仿结果

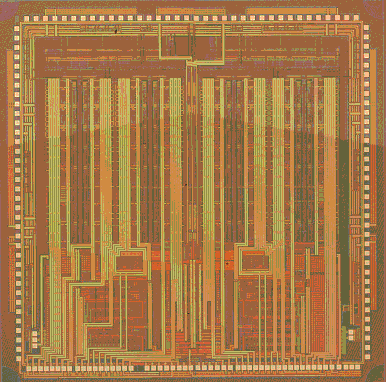

基于0.18 μm BiCMOS 工艺设计的高速宽带采样保持电路应用于8 位高速ADC 中,ADC 版图面积5.256 mm×5.168 mm,如图7 所示。

图7 8位ADC照片图

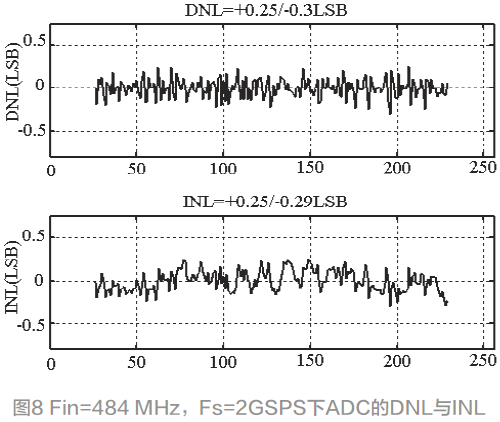

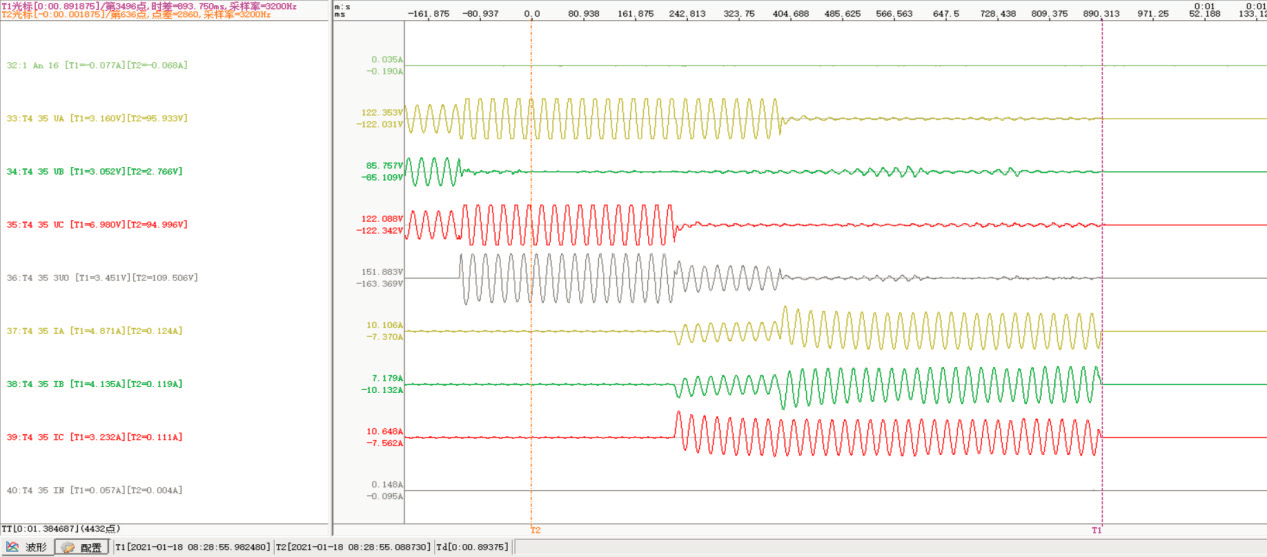

8 位高速ADC 的模拟输入带宽超过2 GHz, 在2GSPS 采样率、50 MHz 模拟输入频率下,如采样保持电路不采用数字校准,则ADC 的有效位只有6 位;如采用数字校准,ADC 的有效位可提升到7.4 位。在2GSPS 采样率、484MHz 模拟输入频率下,启动数字校准,ADC 实测微分非线性DNL ≤ ±0.3LSB、积分非线性INL ≤ ±0.3LSB,如图8 所示。ADC 的SFDR 达到52 dB,如图9 所;有效位为7.32 位。

图9 Fin=484MHz, Fs=2GSPS下ADC的SFDR

5 结论

本文提出的基于0.18 μm BiCMOS 工艺设计的高速宽带采样保持电路,成功应用于8 位高速折叠/ 插值ADC 中,大大提升了ADC 的动态性能与输入带宽。该采样保持电路用开环结构,工作转换速率超过2GSPS,利用增益与失调数字校准算法提升电路的静态和动态性能。ADC 电路测试结果优异,表明设计的高速宽带采样保持电路满足要求。

参考文献:

[1] YU J S, ZHANG R T,ZHANG Z P,et al.A digital calibration technique for an ultra high-speed wide-bandwidth folding and interpolating analog-to-digital converter in 0.18-μm CMOS technology[J]. Journal of Semiconductors,2011,32(1):977.

[2] FLYNN M P,SHEAHAN B.A 400-Msample/s,6-b CMOS Folding and Interpolating ADC[J].IEEE Journal of Solid- State Circuit,1998,33(12):1932.

[3] LEE D, SONG J,SHIN J,et al.Design of a 1.8V 8-bit 500MSPS Folding-Interpolation CMOS A/D Converter with a Folder Averaging Technique[C].18th European Conference on Circuit Theory Design,2007:356.

[4] ALI A M, MORGAN A,DILLON C,et al.A 16 b 250MS/s IF-sampling pipelined A/D converter with background calibration[C].IEEE International Solid-State Circuit Conference Digest of Technical Papers,2010:292.

[5] CHU M, JACOB P,KIM J-W,LeRoy M R,et al.A 40Gs/s Time Interleaved ADC Using SiGe BiCMOS Technology[J]. IEEE Jouurnal of Solid-State Circuit,2010,45(2):380.

(本文来源于《电子产品世界》杂志2022年5月期)

评论