全球首个PCIe 6.0接口子系统 Rambus瞄准高性能SoC应用

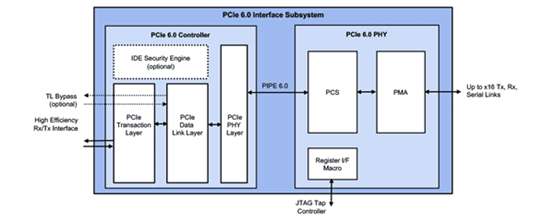

近日,Rambus宣布推出全球首个PCIe 6.0接口子系统,主要面向高性能数据中心、AISoC等领域。Rambus的方案包括完整的PHY物理层、控制器IP,完整符合PCIe 6.0规范,针对异构计算架构全面优化,同时也支持最新的CXL 3.0规范,可优化内存资源。

本文引用地址://m.amcfsurvey.com/article/202301/442687.htmRambus大中华区总经理苏雷介绍,Rambus作为一家业界领先的Silicon IP和芯片提供商,致力于让数据传输更快、更安全。Rambus目前的主要业务包括专利授权、IP授权,以及芯片产品。经过30多年的发展,Rambus有3000多项技术专利,我们的芯片、IP授权主要分为接口IP和安全IP。我们的芯片业务有内存接口芯片。Rambus服务的市场主要面向数据中心、5G、人工智能、IoT和自动驾驶。Rambus面向数据中心应用的主要产品和方案,包括业界领先的DDR5和DDR4在内的内存接口芯片;业界一流的HBM3和HBM2E、GDDR6等内存子系统IP方案;支持PCIe 6.0、5.0、CXL 3.0、2.0接口子系统IP方案;以及支持数据中心、服务器中静态数据、动态数据的加密,实现硬件级的安全IP方案。这些产品和方案极大助力数据中心的应用需求,比如企业级的内存条、AI加速芯片、智能网卡、网络交换机、内存扩展和池化等。

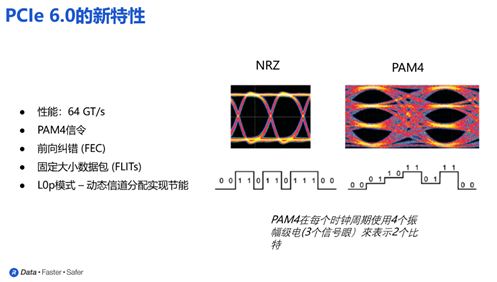

针对新产品PCIe 6.0,Rambus战略营销副总裁Matt Jones介绍最新发布的PCIe 6.0有着非常重要的全新提升,包括数据传输速率可以达到64GT/s,同时支持全新的物理接口以及CXL 3.0。

随着时间的推移,PCIe取得了非常巨大的发展。像大家也都非常熟悉了,从PCIe 1.0推出以来到现在,已经到了PCIe 6.0的时代,可以看到它的数据传输速率都是在上升的。

今年年初,Rambus发布了PCIe 6.0控制器的相关标准,以及具体产品。PCIe 从4.0到5.0到6.0,它的速度是在进一步加快的,其数据传输速率增加幅度也是非常显著。分析背后的原因主要是由于数据爆炸式的增长,而这次数据爆炸式的增长则主要来源于人工智能以及机器学习所驱动的一系列应用。

如果熟悉PCIe数据传输速率每一代之间不同的差异和发展历史,大家应该很容易发现其中的规律,也就是每次推出一个全新版本的PCIe,它的数据传输速率对比上一代基本就是翻倍的。比如PCIe 6.0和上一代的5.0,也就是64GT/s到32GT/s每秒的双倍提升。

PCIe 6.0被认为该标准诞生19年来最具革命性的一次飞跃,不仅数据传输率再次翻番最高可达64GT/s,x16单向带宽128GB/s、双向带宽256GB/s,更是升级为1b/1b编码的PAM4脉冲调制、提升信号完整性和信号稳定性的ECC前向纠错机制、提升高带宽效率的FLIT流量控制单元、更高安全级别的IDE引擎。当然,它依然保持了对PCIe 5.0、PCIe 4.0、PCIe 3.1/3.0的向下兼容。

由于采用了全新的PAM4信令,这也带来了PCIe 6.0时代两大非常重要的改变。第一个改变就是采用前向纠错,必须采用FLITs,就是固定大小数据包作为支持。在这之前的PCIe版本中,是可以支持不同大小的数据包。但由于在PCIe 6.0当中采用了前向纠错,我们也就必须要使用固定大小的数据包,也就是FLITs。

第二个重要的变化就是在PCIe 6.0当中采取的L0p模式。L0p模式的采纳可以让PCIe 6.0实现动态信道分配,更好地达到产品设备的节能。尽管在PCIe各代版本中我们都是有一些选项可以将不使用的信道关闭的,但是L0p模式可以更好地支持动态分配,而动态分配和配置能够帮助我们更好实现节能。

最新发布的PCIe 6.0 PHY是支持CXL 3.0,其数据传输速率可达到64GT/s。Matt Jones表示,由于Rambus采用了PHY和控制器的全集成,从而可以进一步降低延迟,更好的降低功耗,以及优化具体产品和芯片的占用面积。我们的ASIC集成商,包括供应商也无需额外的验证就可以直接将我们的产品应用在他们的产品设计中,通过这种方式无需再去做额外的工作。

Rambus PCIe 6.0接口子系统也搭载了最先进的IDE安全引擎,也就是在我们的控制器当中已经实现了支持,因为随着数据传输速率越来越快,特别是在分布式计算场景之下数据的传输,也就是在PCIe 6.0的环境之下IDE的安全引擎可以保证数据传输的安全性。

评论