KeyStone存储器架构

地址扩展功能可将 32 位地址重新映射到 36 位,从而支持更大的外部存储器。地址扩展能将 DSP 内核中相同的虚拟地址映射到不同的物理地址,并将多个虚拟地址映射到同一物理地址,这对于同一个存储器来说具有不同的语义。MPAX 单元可将运行在不同 DSP 内核之上的操作系统和应用进行隔离,并能轻松支持共享程序。

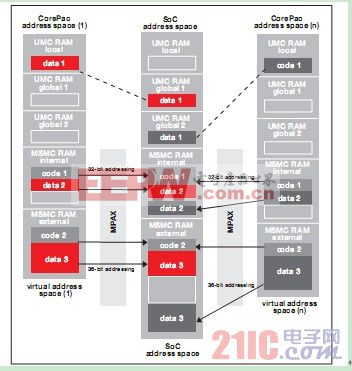

图 6 显示了如何在KeyStone架构内使用 MPAX 来构建多内核虚拟存储器的实例。假定所有内核均运行同一应用,则可将该共享程序和静态数据加载至共享的内部和外部存储器区域中。私有变量(如数据 1)可以使用各个内核中的同一虚拟地址,同时 MPAX 将其映射至不同的物理存储器地址。软件在运行时无需重新进行任何地址映射即可使相同的代码映像在多个内核上执行。

错误检测与校正 —— 专用于基础局端系统的数代 C6000 器件系列,内部存储空间中包含了软错误校正功能。KeyStone系列器件以该技术为构建基础,能够进一步将软错误保护扩展至存储器的所有层级。

图 6 - 多内核虚拟存储器

层级系统中的存储器控制器可支持多级保护,并可用于实现对代码段进行全面校正,并对数据空间进行错误检测。L1P、L2 和 SL2(或 SL3 内部 RAM)均包含可用于检测和校正 128 位或 256 位存储器段内单个位错误的奇偶校验信息。另外,我们还将能检测到同一访问中的两个位错误并触发访问 CorePac 产生异常。对于数据存取,仅能检测到位误差,并触发异常。无论发生检测还是校正事件,信息均被存储在错误访问的存储器控制器中,以便为应用和/或主机恢复提供信息援助。

通过 ECC 逻辑可将软错误保护进一步扩展至外部存储器空间。每 64 位数据有一个 8 位 ECC 码,根据选项可配置成支持 32 位和 64 位数据宽度。添加 ECC 需要支持 32 位数据宽度的额外 4 位 DDR3 IC(实现 36 位接口),或额外的 8 位 DDR3 IC(实现 72 位接口)以存放与整个外部数据空间相关的 ECC 值。

总结新型KeyStone架构在存储器架构方面具备各种优势,意味着无论在单内核还是在多内核 SoC 执行环境中都能够直接实现显著的性能提升。与此前的产品系列相比,这些性能提升涉及各级存储器,如局域 L2、共享 L2/L3,以及外部存储器等。通过高效判优和预取机制,性能改进也体现在多内核、加速器以及数据 I/O 的并行访问方面。

针对内核之间以及内核与数据 I/O 之间的共享数据页面,缓存一致性控制的改进可实现更简单的判优。

实施存储器保护和地址扩展可实现高度灵活的编程模型、更大范围的地址搜索并为错误访问提供保护。

针对各级存储器的软错误保护可确保运行时执行不受随机软错误事件的影响,而这一事件会对所有嵌入式处理器造成影响。

Keystone 架构在存储器性能、易操作性以及灵活性方面实现的改进可确保程序员能够实现由功能强大的新型C66X DSP系列提供的全速性能优势。该架构具有卓越的可扩展性,其为具有各种数量的内核、加速器和数据 I/O 的 SoC 系列奠定了坚实基础,。

评论