基于USB的数据采集系统的设计与研究

3.1USB控制器外围电路设计

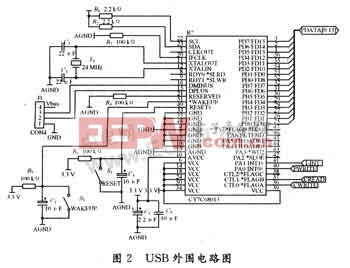

USB控制器及其外围电路组成了系统的数据读取和传输模块,这部分主要负责读取和传输ADC转换后的数据,并负责与PC机的通信,从而完成这个系统的功能。由于CY7C68013把多重功能都集成到一个片子上,所以外部电路显得不是很复杂,与一般的电路比较,减少了电路复杂的外部数据线和信号线的连接,有利于提高整个系统的可靠性[4]。LISB控制器部分外围电路原理图如图2所示。

CY7C68013用自己的片内晶振电路和一个外部24 MHz晶振组成系统的时钟电路。他有一个片内锁相环(PLL)电路,利用PLL可以把24 MHz振荡器频率倍频至480 MHz供收发器使用。内部计数器把24 MHz的频率分频为内部8051需要的默认的12 MHz的时钟频率。XTALIN和XTALOUT分别为晶振的输入和输出引脚,分别与晶振相连,同时,晶振的两个引脚分别通过一个20~33 pF的负载电容接地。DMINUS和DPLUS为USB的D+,D一信号线,分别和LISB连接器的相应引脚相接。LJSB连接器上的VBUS和GND为总线电源线,整个系统的所需要的各种电压都是通过该电源转换而得到。SCL和SDA分别为I2C总线的时钟线和数据线,在本设计中,系统的固件程序采取从主机下载的方法。因此,这里无需连接外部E2PROM,这两个引脚要分别通过一个2.2 Ω的电阻连接到电源引脚VCC上。RESERVED引脚为芯片的保留引脚,通过一个2.2 Ω接地。

RESET引脚为芯片的复位引脚。该引脚有一个滞后作用并且低电平有效。因为内部锁相环在VCC升至3.3 V后大约200 μs保持稳定,所以,RESET引脚所连接的外部RC网络要取适当的值来满足这个需要,典型的取值为:R-100 kΩ,C=0.1μF。wAKEUP为唤醒引脚,在805l和芯片的其他部分为低功耗状态时,USB系统挂起,PLL和晶振停止工作,当外部逻辑触发wAKEUP,晶振重新工作之后,PLL趋于稳定,同时,8051也会收到一个唤醒中断。RDY0,CTLO,CTL1引脚分别和对应ADC及其外围电路的接口相连,FD[15:0]分别和ADC的对应数据线连接。

3.2 A/D采样通道设计

本文采用的是CY7C68013的GPIF工作模式,因此直接利用了GPIF的16位并行接口,这样每次可以按字(2个8位)读取数据。考虑到ADC0804的廉价,并且省去了连接多路选择器和其相关的控制接口电路等因素,提高系统的可靠性,利用2片AI)C0804同时与GPIF接口相连接,避免了利用多路开关时的所需的转换时间m56,在程序部分,也省去了选择模拟信号通道部分。

3.3 电源电路设计

在本设计中,需要3种大小不同的供电电源,除了ADC0804需要的+5 V供电电源外,还有CY7C68013需要的+3.3 V的供电电源,模数转换器ADC0804需要的+2.5 V的基准电压电源。由于整个系统可以使用总线电源供电,不需要外加电源,因此需要把+5 V的总线电源转换为系统各个部分所需的电源。+3.3 V电源是CY7C68013所需芯片供电电压。设计中,选用的是MAxIM公司的电源转换芯片MAX882n 0,连接电路如图3所示。

评论