将音频编解码器植入28nm高级移动多媒体芯片系统

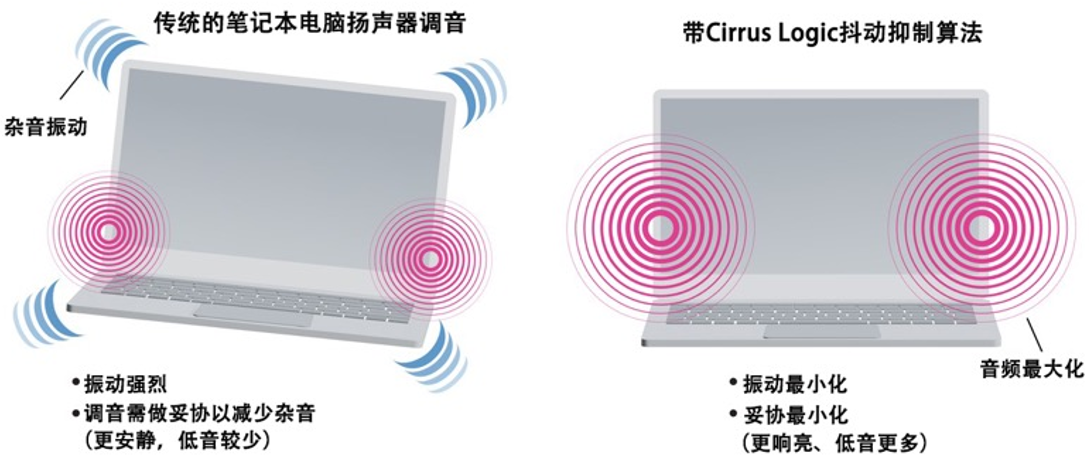

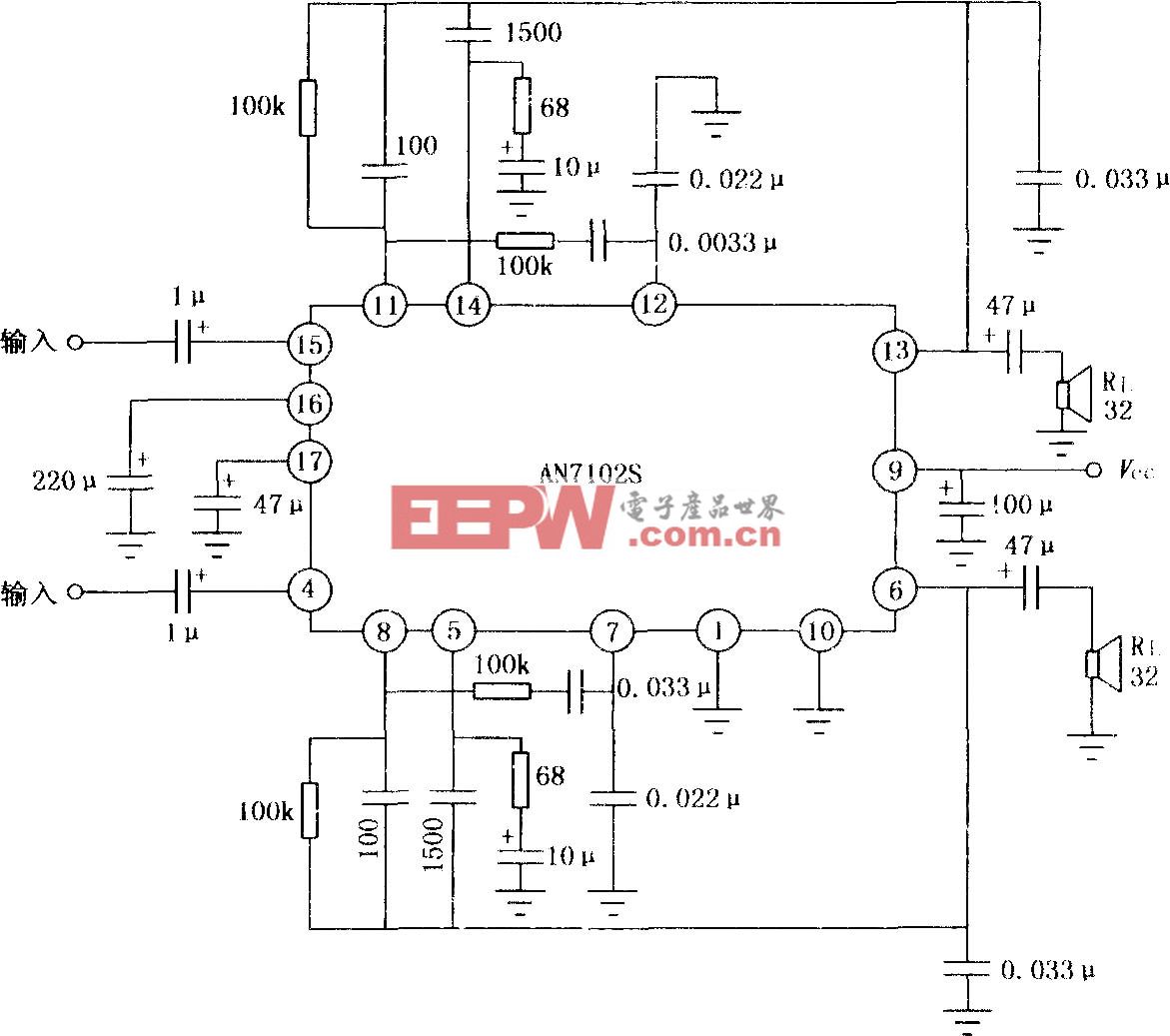

通过将更多信号处理从模拟域迁移到数字域,音频编解码器可提高符合摩尔定律的数字电路比例,并减少模拟电路比例。这产生了以数字为中心的新架构。在这种新架构中,所有信号处理都在数字模块执行,周边模拟电路包括数据转换器和异步采样速率转换器(ASRC),见图2。ASRC技术将在下一部分详细介绍。

现代移动多媒体系统有可能有多个数字主控,全部在各自的时钟域运行。例如,基带处理器将管理与蜂窝式无线电的通讯,应用处理器将管理来自系统闪存的媒体文件,而蓝牙集成电路(IC)可连接数量不限的蓝牙周边设备。每个数字主控都分别按照异步时钟速率运行。因此,这一系统中的音频编解码器不仅在数字域和模拟域之间架起了桥梁,而且还在数字生态系统中不同时钟域之间进行互动通讯。

图2:伴随数字音频主控进行以数字为中心的音频处理

灵活设计支持多个时钟速率

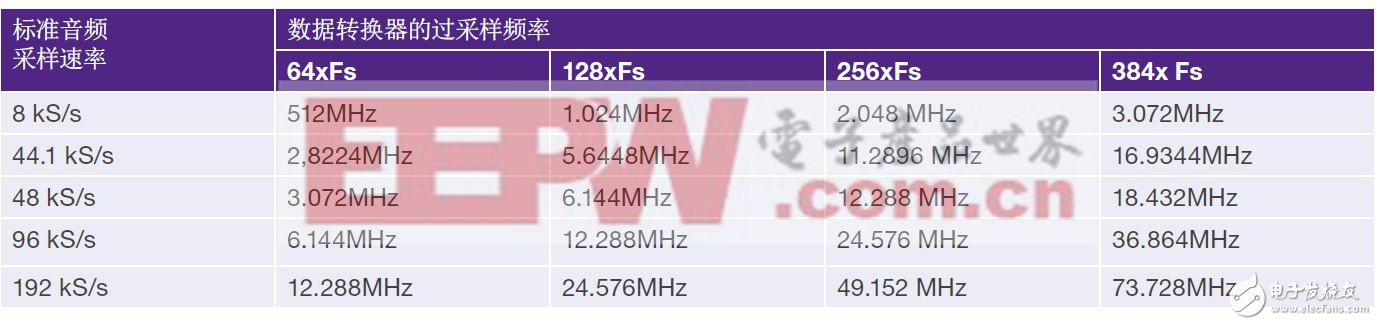

大量数字主控和时钟域给音频编解码器,特别是对高度集成的28纳米芯片系统造成了又一个挑战。按不同标准速率对数字音频采样,如表1所示。音频编解码器上数据转换器要求的时钟取决于音频数据采样速率和主机应用于芯片系统上的时钟。由于存在多种音频采样速率和各种主机时钟,它们的组合相当复杂。数字滤波器可为解决这一问题发挥重要作用,原因是它们可以处理数字音频接口和音频数据转换器之间的数据采样,因此能够进行采样速率转换。

表1:标准音频采样速率

由于数据转换器必须以过采样频率(通常是128X和256X)运行,驱动数据转换器所需的主时钟频率介于5-12MHz范围。因此,音频编解码器必须支持各种不同的音频采样速率,并适应主时钟频率,便于其在应用中集成。但是,由于存在多种时钟频率比率的组合与制约,这个目标实现起来并不直接。因此,数字滤波器必须包括采样速率转换配置。表2是音频采样速率和采样速率转换不同组合的常用采样频率。

表2:音频采样速率和采样速率转换不同组合的常用采样频率

为了适应所有数据速率和可用时钟的组合,设计人员可采用各种技巧,详见下一部分。

技巧1:音频时钟使用锁相环路

由于一些条件如空间和/或成本的限制,许多应用无法使用音频编解码器专用的晶体振荡器。音频编解码器必须能够支持现有主机主时钟的不同音频速率(通常是USB时钟的12MHz或它的倍数)。锁相环路(PLL)可用于生成所需要的音频时钟。由于要求非常好的频率分辨率以支持所有频率组合且,同时要提供低抖动输出时钟,这对锁相环路的性能要求超出了一般标准,而且。因此,最好采用不要求锁相环路的其他解决方案。

技巧2:重复使用没有锁相环路的USB时钟

一种替代解决方案是采用没有锁相环路的技术,即重复使用USB时钟和避免为音频添加专用锁相环路。USB是非常很受欢迎的接口,几乎是普遍存在于所有应用中。12MHz或24MHz的时钟都可使用,它们的抖动相对较低,而这是音频的重要要求。24MHz USB时钟可支持48kS/s音频速率及其倍数的音频速率,如96kS/s和192kS/s,因为它是整数倍数(24,000=125x192)。要使用24MHz USB时钟,需要将滤波器采样速率转换从标称的128倍重新配置为125倍。<

评论