基于SystemView的数字频率合成器的设计

在SystemView环境下的操作比较简明,根据系统设计要求利用SystemView本身提供的各种函数图符建立仿真模型,并对其进行参数设置,在设定系统运行时间等参数后就可进行仿真分析。

3数字频率合成器的设计与仿真

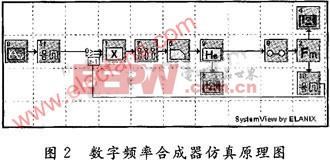

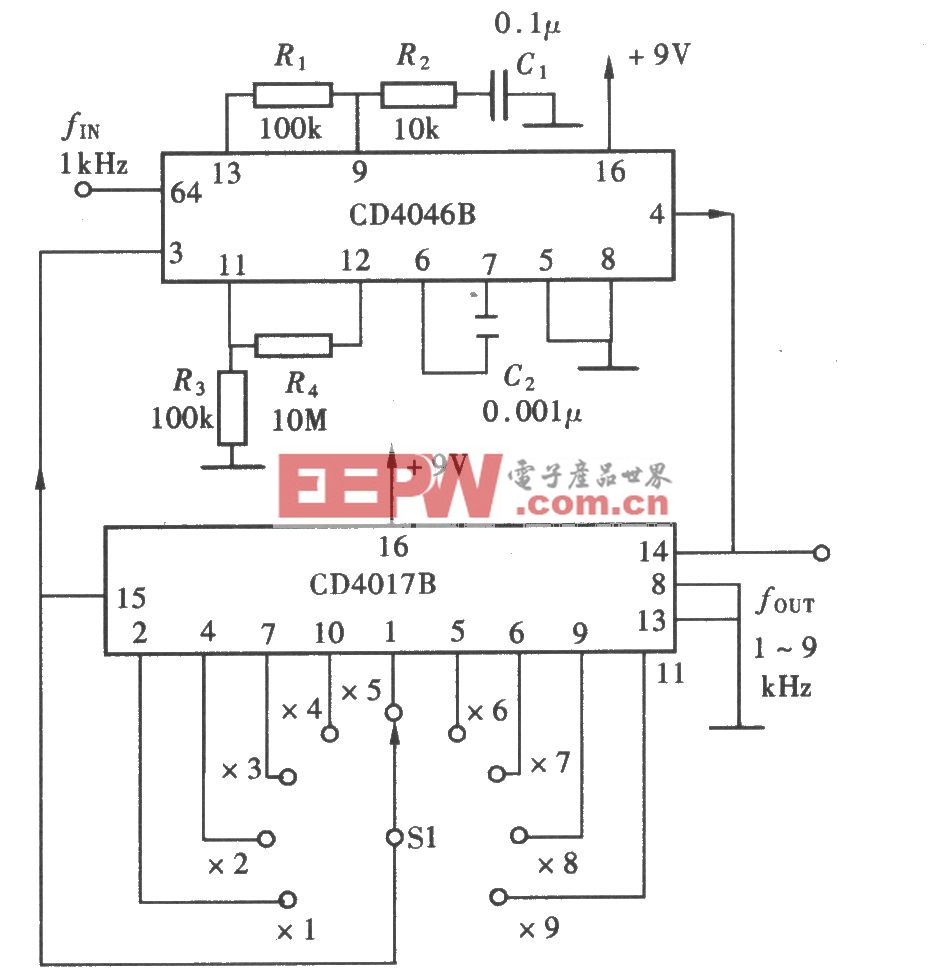

基于以上对数字频率合成器的分析,在SystemView设计环境下,建立了典型的数字频率合成器的模型,如图2所示。在此模型中,锁相环的VCO用FM图符(图符2)代替,其载波频率设置为195 Hz,增益为20 Hz/V,环路低通滤波器使用了一个8极点的贝塞尔低通滤波器,带通为5 Hz,分频器使用通信图符中的N倍分频器,根据锁相环的输出特性,若分频比N=20,则锁相环的输出频率fo应该锁定在fo=N·fR=20·fR频率上。

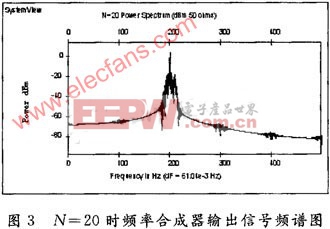

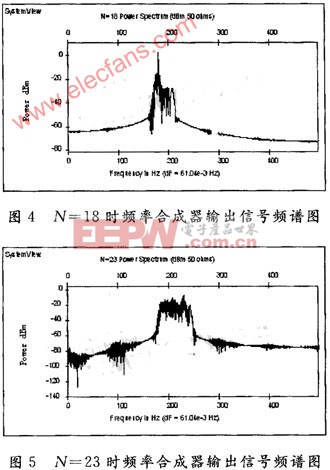

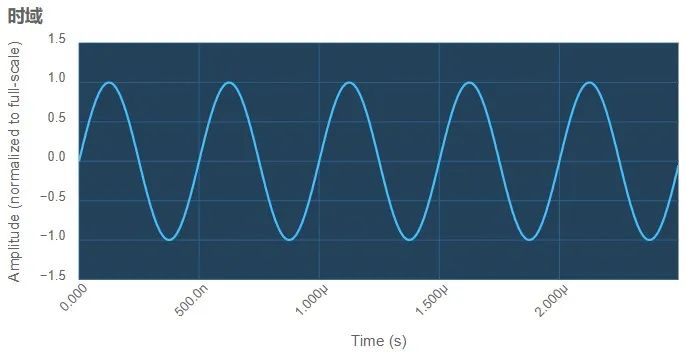

假设输人参考振荡器1 kHz,进行100分频后作为基准频率进入到数字频率合成器中,也即基准频率为fR=10 Hz,在系统时间参数设定为1 000 Hz,采样点数为16 384点情况下,对构建的系统进行仿真,当N=20时,由图3输出信号的频谱图可以看出,在频率为200 Hz处出现了较高的频谱能量峰值,这说明输出信号的频率被锁定在200 Hz。当把N改为18时,输出信号的频谱在频率为180 Hz附近处出现了能量高峰值,如图4所示,同理说明此时输出信号的频率处于锁定状态。

|

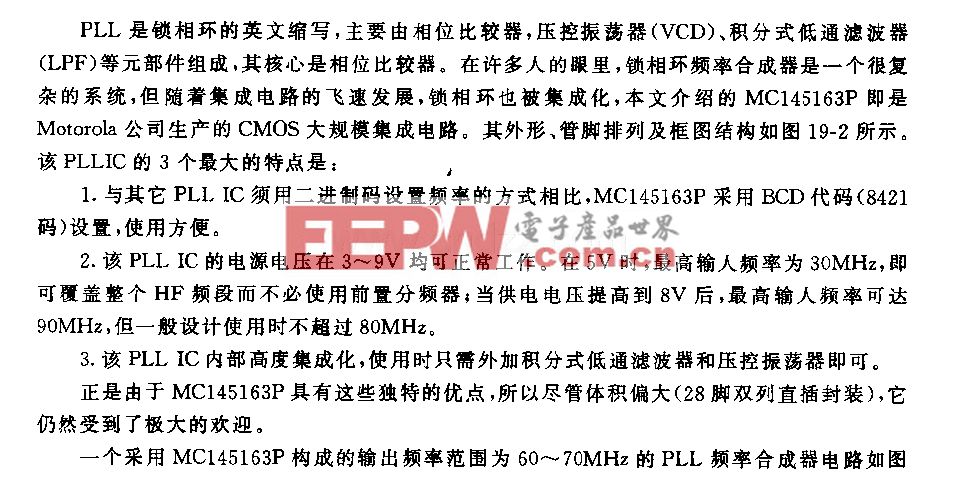

由以上仿真分析可以看出,改变N的值,输出信号的频率将变为基准频率10 Hz的整数倍。但事实上由于锁相环的锁定范围限制(与滤波器带宽和VCO的载波最大变化范围有关),只能输出VCO载波频率附近的几个整数倍的频率。当N=23时,输出信号频谱如图5所示,图中频谱能量高峰值并不像以上图示那么清晰,而是存在能量高峰区,由此说明输出信号频率比较平均地分布在180~240 Hz频带内,此时的锁相环处于失锁状态,频率合成器也失去了作用。因此,在进行分频比设置时,N值不能设置太高。在实际应用中,特别在超高频工作情况下,为获得较大范围的频率选择(较多的频率数)和较小的步进频率,多采用吞食脉冲式锁相环频率合成器。

4 结 语

混频器相关文章:混频器原理

鉴相器相关文章:鉴相器原理

锁相环相关文章:锁相环原理

评论