基于PCB模拟设计的良好接地指导原则

由于实际机械设计的原因,电源输入连接器在电路板的一端,而需要靠近散热器的电源输出部分则在另一端。电路板具有100 mm宽的接地层,还有电流为15 A的功率放大器。如果接地层厚0.038 mm,15 A的电流流过时会产生68 μV/mm的压降。对于任何共用该PCB且以地为参考的精密模拟电路,这种压降都会引起严重问题。可以割裂接地层,让大电流不流入精密电路区域,而迫使它环绕割裂位置流动。这样可以防止接地问题(在这种情况下确实存在),不过该电流流过的接地层部分中电压梯度会提高。

在多个接地层系统中,请务必避免覆盖接地层,特别是模拟层和数字层。该问题将导致从一个层(可能是数字地)到另一个层的容性耦合。要记住,电容是由两个导体(两个接地层)组成的,中间用绝缘体(PC板材料)隔离。

具有低数字电流的混合信号IC的接地和去耦

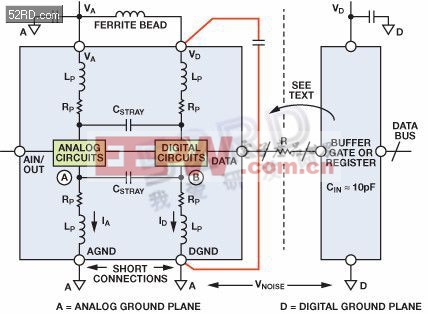

敏感的模拟元件,例如放大器和基准电压源,必须参考和去耦至模拟接地层。具有低数字电流的ADC和DAC(和其他混合信号IC)一般应视为模拟元件,同样接地并去耦至模拟接地层。乍看之下,这一要求似乎有些矛盾,因为转换器具有模拟和数字接口,且通常有指定为模拟接地(AGND)和数字接地(DGND)的引脚。图4有助于解释这一两难问题。

同时具有模拟和数字电路的IC(例如ADC或DAC)内部,接地通常保持独立,以免将数字信号耦合至模拟电路内。图4显示了一个简单的转换器模型。将芯片焊盘连接到封装引脚难免产生线焊电感和电阻,IC设计人员对此是无能为力的,心中清楚即可。快速变化的数字电流在B点产生电压,且必然会通过杂散电容CSTRAY耦合至模拟电路的A点。此外,IC封装的每对相邻引脚间约有0.2 pF的杂散电容,同样无法避免!IC设计人员的任务是排除此影响让芯片正常工作。不过,为了防止进一步耦合,AGND和DGND应通过最短的引线在外部连在一起,并接到模拟接地层。DGND连接内的任何额外阻抗将在B点产生更多数字噪声;继而使更多数字噪声通过杂散电容耦合至模拟电路。请注意,将DGND连接到数字接地层会在AGND和DGND引脚两端施加 VNOISE ,带来严重问题!

“DGND”名称表示此引脚连接到IC的数字地,但并不意味着此引脚必须连接到系统的数字地。可以更准确地将其称为IC的内部“数字回路”。

这种安排确实可能给模拟接地层带来少量数字噪声,但这些电流非常小,只要确保转换器输出不会驱动较大扇出(通常不会如此设计)就能降至最低。将转换器数字端口上的扇出降至最低(也意味着电流更低),还能让转换器逻辑转换波形少受振铃影响,尽可能减少数字开关电流,从而减少至转换器模拟端口的耦合。通过插入小型有损铁氧体磁珠,如图4所示,逻辑电源引脚pin (VD) 可进一步与模拟电源隔离。转换器的内部瞬态数字电流将在小环路内流动,从VD 经去耦电容到达DGND(此路径用图中红线表示)。因此瞬态数字电流不会出现在外部模拟接地层上,而是局限于环路内。VD引脚去耦电容应尽可能靠近转换器安装,以便将寄生电感降至最低。去耦电容应为低电感陶瓷型,通常介于0.01 μF (10 nF)和0.1 μF (100 nF)之间。

再强调一次,没有任何一种接地方案适用于所有应用。但是,通过了解各个选项和提前进行规则,可以最大程度地减少问题。

小心处理ADC数字输出

将数据缓冲器放置在转换器旁不失为好办法,可将数字输出与数据总线噪声隔离开(如图4所示)。数据缓冲器也有助于将转换器

评论