基于GAL的I2C总线时序模拟

FI1200 MK2系列电视信号前端处理器是飞利浦公司专为计算机多媒体环境下的射频应用而设计的。FI1256 MK2是该系列中的一个型号,它体积小,结构紧凑,性能稳定,可直接从射频信号解调出视频信号和音频信号,且只需单一5V电源,因而可在图文电视接收、有线电视信号自动监测等许多场合得到广泛的应用。笔者曾用它开发出图文电视接收卡、电视信号检测系统等多种设备。

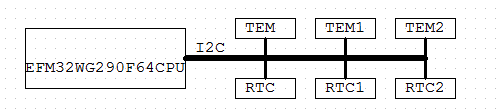

FI1256 MK2可通过I2C串行总线接口进行编程控制。当使用单片机进行编程控制时,带有I2C接口的单片机可以与FI1256 MK2直接连接,没有I2C接口的单片机可以用I/O口线模拟I2C总线的时序。但是FI1256 MK2在计算机扩展卡中使用时,为了节省成本,通过计算机的总线直接对其进行编程控制时,就需要用计算机的总线模拟出I2C总线的时序。本文给出了用可编程逻辑器件GAL配合ISA总线模拟I2C总线时序来对FI1256 MK2进行控制的方法。该方法与PCI总线进行模拟的方法相类似。

1 I2C总线操作方式

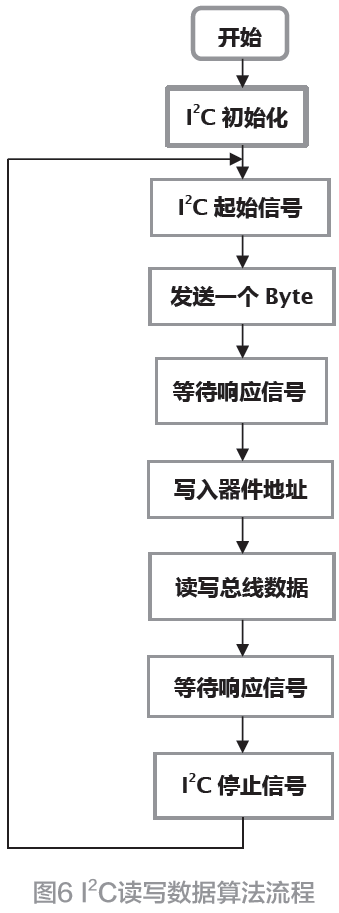

I2C总线是被广泛应用的串行多主控器总线,它可以让多个有控制总线能力的器件连接到总线上。I2C总线通过串行数据(SDA)和串行时钟(SCL)两条线使连接在该总线上的器件进行数据传输,每个器件的识别由一特定地址确定。除了作为发送器和接收器外,该器件还可以被设定为主控器和被控器。主控器用于启动总线上的数据发送,并产生数据传输所需的时钟信号,其他被寻址的器件均认为是被控器。SDA线和SCL线都是双向传输线,它们各通过一个上拉电阻连接到正电源。当总线处于空闲状态时,两条线均处于高电平。连接到总线的器件输出级必须是集电极开路或漏极开路,以用来产生“线与”功能便于多个器件的接入。在标准方式下,I2C总线上的数据传输速率可达100kbps,在快速方式下则可达到400kbps。连接到总线上的器件数量只受400pF的总线电容的限制。进行数据传输时,SDA线上的数据在SCL为高电平期间必须是稳定的,只有在SCL线上的时钟信号为低时,数据线上的状态才可以改变。当SCL线保持高电平时,通常把SDA线上由高到低和由低到高的电平变化分别定义为开始条件和停止条件。主控器启动数据传输时,总是先给出开始条件,然后传输若干字节的数据,最后给出停止条件以结束一次数据传输过程。图1是带有开始和停止条件的只传输一个字节的总线时序。

2 模拟I2C总线时序

可编程逻辑器件是近二十年发展起来的专用集成电路的一个分支,是设计新型数字系统的理想器件。它不仅速度快,集成度高,而且具有用户可定义的逻辑功能,有的还可以加密,并可以重复编程,因此,它不仅能适应各种应用需要,而且可以大大简化硬件系统,降低成本,提高系统的灵活性、可靠性和保密性,所以,近年来得到了迅速的发展。在各种可编程逻辑器件中,以CPLD功能最为强大,但价格较高,使用也较为复杂。而GAL不但有相当强的功能和足够的灵活性,而且编程控制容易(可使用普通的编程器),价格很低,接近通用集成电路,故在数字逻辑不是非常复杂的系统中使用GAL是非常合适的。

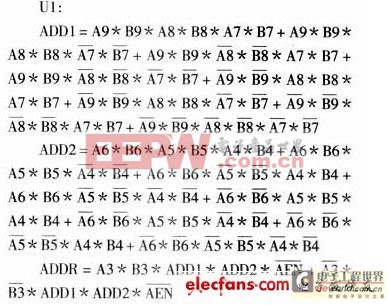

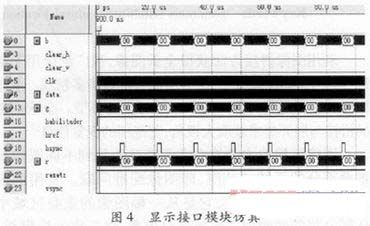

用计算机的ISA总线对FI1256 MK2进行编程控制时,可以将FI1256 MK2作为一个外设,然后用两根数据线模拟SCL和SDA。需要注意的是:由于计算机速度高,总线周期短,达不到I2C总线的定时要求,因此要在总线周期过后进行延时,这样总线上出现的高阻状态或与其它设备的通信数据就会破坏I2C的时序,所以应将SDA和SCL的状态锁存,以满足I2C总线的定时要求。图2是用GAL实现ISA与I2C接口电路的设计方案。由于对FI1256 MK2的操作一般只是写入编程控制字节,因此,为简单起见,该电路只用来实现将计算机作为主控器的写操作时序。

评论