嵌入式微控制器MC68HC912B32背景调试模式设计及实现

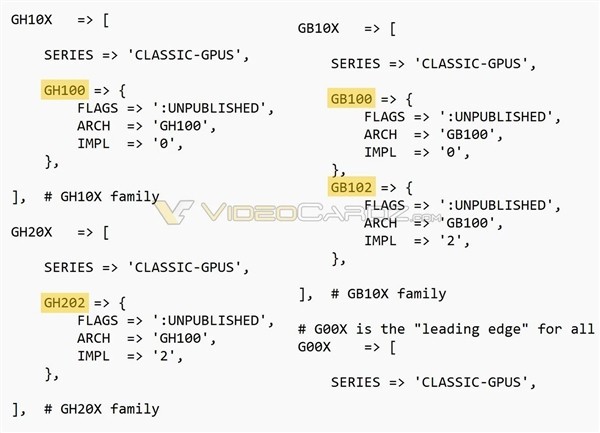

随着flash技术在微处理器上的广泛应用,使单片机在开发和应用手段上有了革命性的变化,从传统的仿真器(ice)到目前流行的jtag,设计人员在不断寻找一种移植性更高、更易操作、费用更低的开发手段。使用传统的仿真器进行嵌入式开发时,通常调试工具会受价格和烦琐的操作所限制,但是随着微处理器制造工艺的提高及flash技术的发展,一些高端微处理器(如cpu12/16/32、powerpc、coldfire等)内部已经包含了用于调试的微代码,并可以通过背景调试模式bdm(background debug mode)进行调试,由于这种方法省去了仿真器,因此避免了高频操作、交直流电不匹配等问题,随着bdm标准的不断规范和普及,用bdm调试模式进行嵌入式开发已经成为一种首选。

mc68hc912b32(以下简称b32)是由freescale公司推出的一款基于cpu12核心的16位嵌入式mcu。它具有体积小、功耗小、功能多等优点,主要用于汽车电子、工业控制、医疗设备等领域,它是freescale公司较早提供的一款背景调试模式的16位mcu。背景调试模式是freescale公司自定义的片上调试规范。

1 背景调试模式介绍

bdm是由freescale半导体公司推出的一种单线(single wire)调试方式,是目前单片机普通采用的调试方式之一。其他公司的嵌入式处理器也有类似的调试方式,如amd公司的x86μp系列微处理器提供的amdebug调试方式等。

bdm调试方式为开发人员提供了底层的调试手段,开发人员可以通过它初次向目标板下载程序,同时也可以通过bdm调试器对目标板mcu的flash进行写入、擦除等操作,用户也可以通过它进行应用程序的下载和在线更新、在线动态调试和编程、读取cpu各个寄存器的内容、单片机内部资源的配置与修复、程序的加密处理等操作,而这些仅需要向cpu发送几个简单的指令就可以实现,从而使调试软件的便携变得非常简单,通常自己就可以编写,bdm硬件调试插头的设计也非常简单,关键是要满足通信时序关系和电平转换要求。

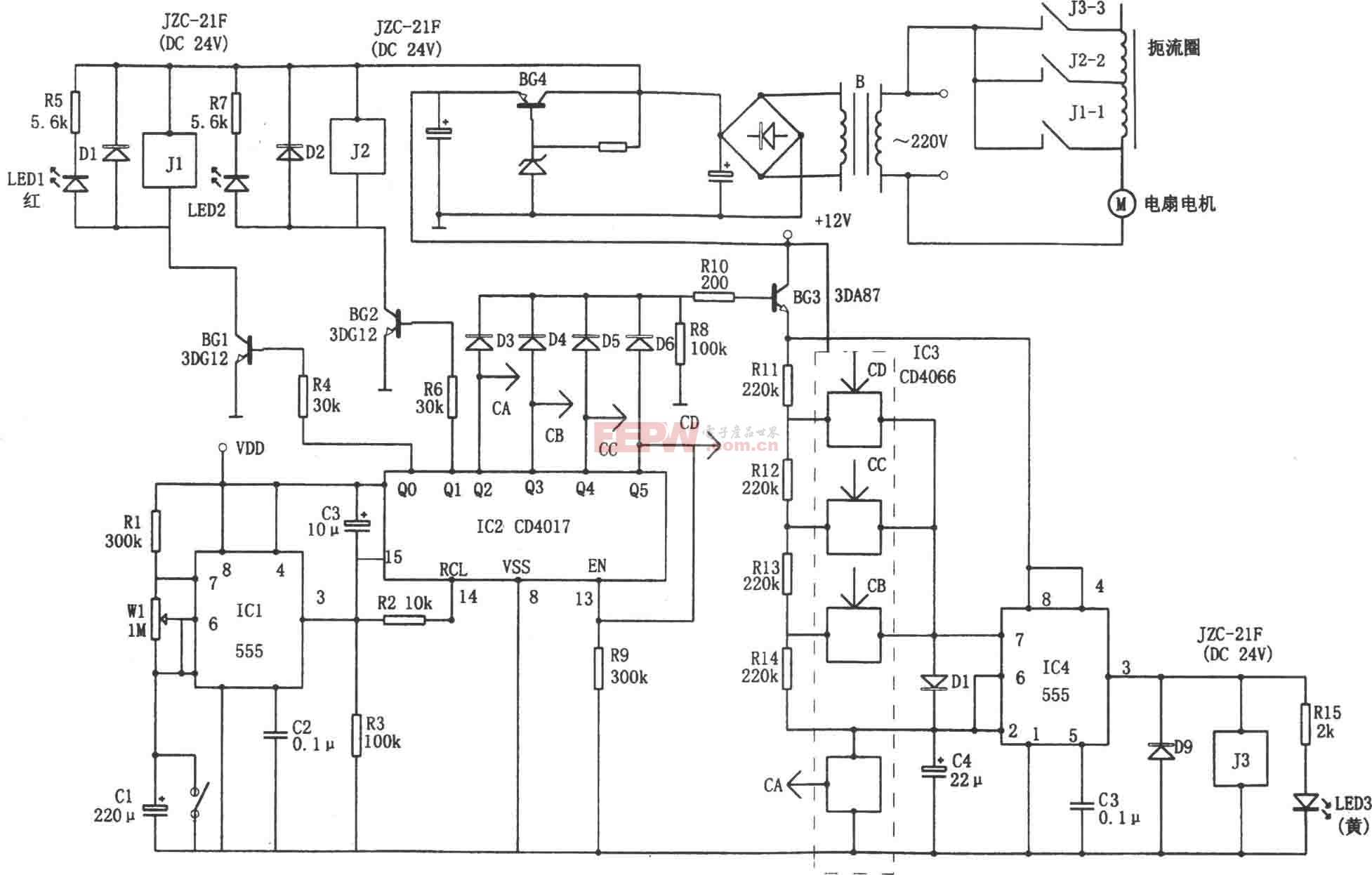

目前常用的标准bdm调试插头如图1所示,各个引脚信号的定义如表1所示。

2.1 总体概述

以cpu12为内核的mcu的运行模式有单片方式(single chip)和扩展方式(expanded mode)两种。运行模式主要由bkgd、modb和moda引脚的状态决定,各个模式与引脚状态间的关系见表2。单片模式又分普通单片模式(normal single chip)和特殊单片模式(special single chip)两种,而只有在特殊模式下bdm才能被激活,因此特殊单片模式又称bdm模式。图2为pc机通过bdm插头与目标机相连。

2.2 bdm指令介绍

bdm有两类指令。一类是在一般运行模式下可以直接执行的,被称为硬件指令(hardware command);另一类则是只能在bdm模式下执行的程序,这些程序在进入bdm模式后被固化在地址为﹩ff00-﹩ffff的rom中,被称为固件指令(firmware command)。

因为bdm控制模块不在cpu中,所以bdm硬件指令可以在cpu正常运行时被并行执行,其他bdm指令是基于固件的,必须在cpu处于bdm模式下才能执行。硬件指令允许读写目标系统内(包括片内ram、eeprom、i/o控制寄存器等)的所有内存。硬件指令可以不在bdm模式下执行,表3列出了bdm模块常用的硬件指令。

固件指令必须在hc12单片机的bdm rom中执行,且cpu必须在bdm模式下才能执行,通常使用硬件指令background使cpu进入bdm模式,当bdm被激活时,bdm rom就被分配到地址空间:﹩ff20-﹩ffff,同时7个bdm寄存器被分配到地址空间:﹩ff00-﹩ff06,此时cpu就可以通过执行rom中的代码完成相应的固件指令操作。表4列出了bdm的7个寄存器,表5介绍了常用的3个固件指令。

2.3进入bdm模式

下面介绍使目标机进入bdm模式的两种常用方法。

方法1:将目标机的bkgd引脚拉低,然后给目标机的reset引脚加低电平,即给目标机复位,复位脉冲要足够宽,至少要大于目标机的512个时钟周期。本文采用freescale公司的8位微处理器mc68hc908jb8(简称jb8)制作bdm调试头,用其pta0和pta1口控制目标机的reset和bkgd引脚,此方法通过软件编程的方式进入bdm模式。

方法2:通过硬件跳线的方式将bkgd置低电平,在目标机复位后再将bkgd置高电平,以进入目标机的bdm模式。进入bdm模式后,带有bdm程序的片内专用rom将flash的﹩ff00-﹩ffff替换,此空间在普通单片方式下存放中断向量。该方法仅通过硬件跳线的方式进入bdm模式。

3 b32的bdm调试系统设计

3.1 bdm调试其系统硬件设计

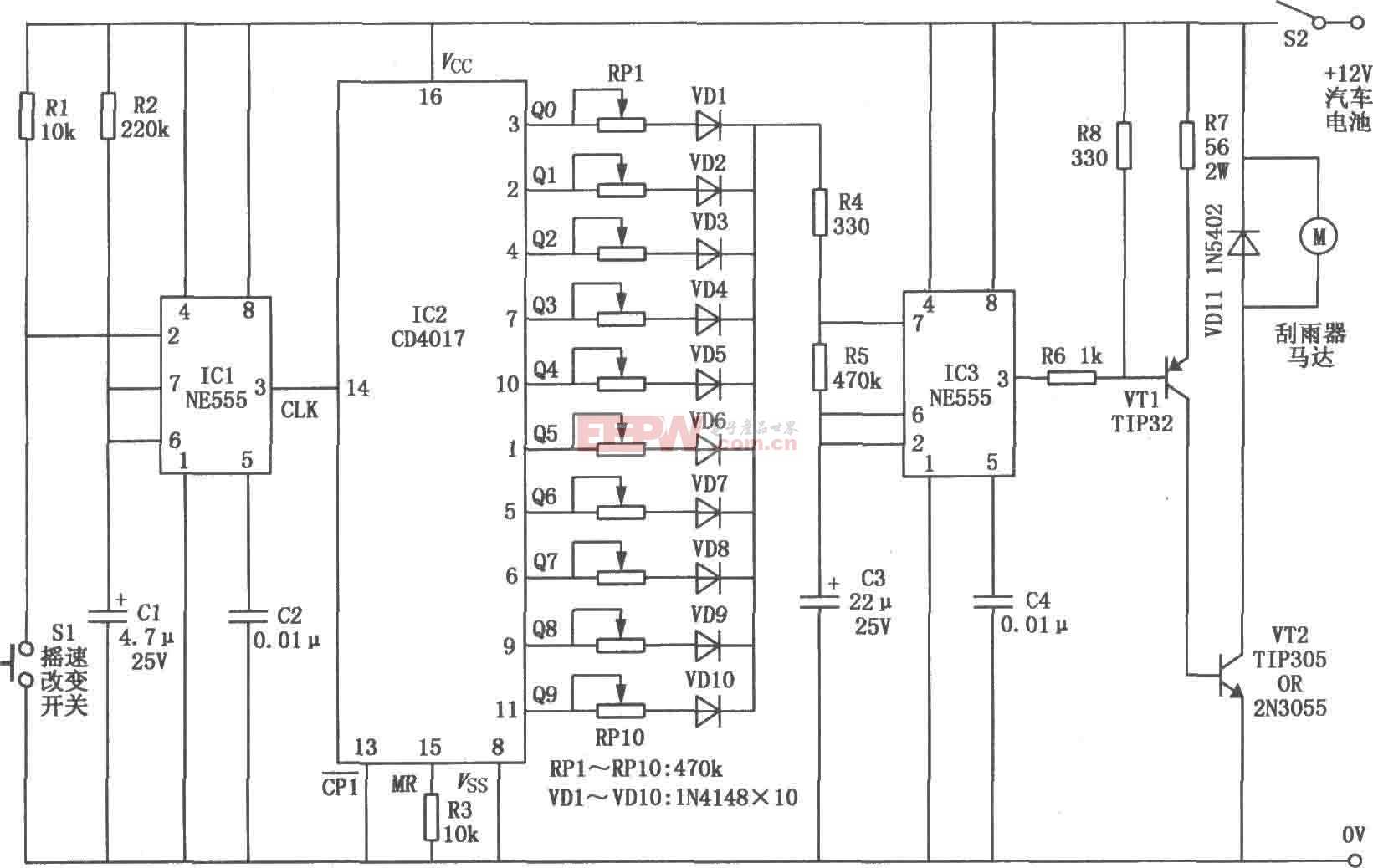

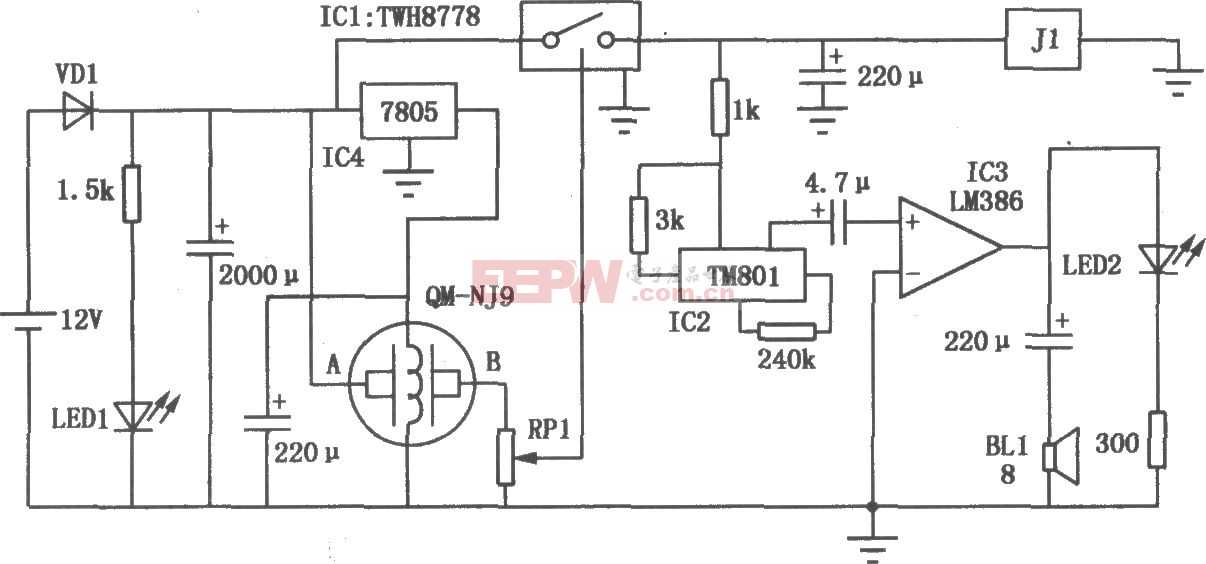

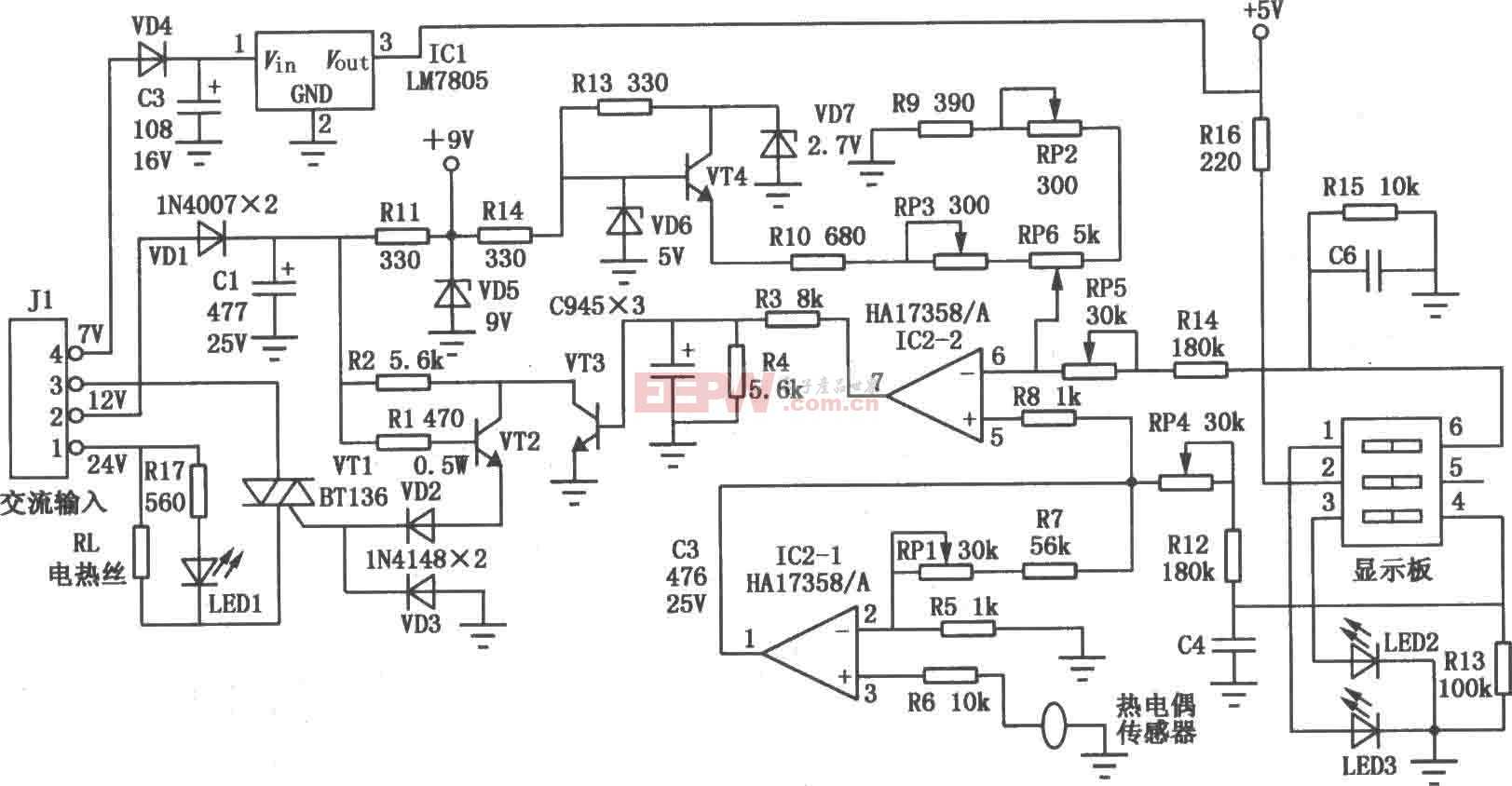

该bdm调试器的bkgd和reset信号分别由jb8单片机的i/o口pta1、pta0提供。双方通信引脚使用漏极开路驱动(或称线或)的方式,平时靠上拉电阻维持高电平。flash编程电源vfp由max662提供,max662是一款专门提供12v flash编程电压的芯片。max662外围电路原理图如图3,bdm调试插头电路原理图如图4。

3.2 bdm调试器系统软件设计

cpu12的bdm通信协议也称为单线通信协议。下面按照该协议,以jb8作为主控制芯片详细介绍b32的bdm调试系统的软件设计。在程序开始前,需要宏定义一些常量以方便下面程序的调用。具体的宏定义有:

3.2.1 调用读写汇编子程序

通过调用读写汇编子程序,可以读取和发送一个字节,具体函数如下:

调用写子程序的输入参数是需要被写的一个字节,调用读子程序的返回参数是读取到的一个字节。

3.2.2 读写汇编子程序

主机方以下降沿通知目标机方的bkgd端,位通信开始,每一位传输至少需要16个时钟周期。具体过程如下:

主机首先拉低bkgd引脚,并时低电平维持时间不短于512个时钟周期,目标机探测到下降沿信号后清命令寄存器,同时等待接收主机的bdm命令。

主机写位0到目标机bkgd端的操作为:主机拉低目标机的bkgd端不少于12个时钟周期,目标机在探测到低电平以后的第10个周期对bkgd采样,读入该位的0。

主机写位1到目标机bkgd端的操作为:主机拉低目标机的bkgd端2-4个时钟周期后释放bkgd端,使之为高电平,目标机在探测到低电平以后的第10个周期对bkgd采样,读入该位的1。

下面是写一个字节的汇编代码:

主机读目标机bkgd端的信息时,主机拉低目标机bkgd端2-4个周期后释放bkgd端,然后定义该引脚为输入状态,读取bkgd端的电平,如果目标机输出为0电平,则继续拉低bkgd端,从探测到主机拉低bkgd端起持续13个时钟周期,所以主机的读操作应在从拉低bkgd线算起的13个时钟周期内完成,对于目标机输出为1的情况,无需目标机输出高电平,因为bkgd端已用电阻上拉,只需定义该引脚为输入,则自然会使之为1。

下面是读取一个字节的汇编代码:

对于硬件命令,命令之间间隔要大于150个时钟周期,对于固件命令,送出读命令到读取数据之间要延迟32个时钟周期,写命令后面可紧跟需要写的数据,但与下一条命令之间要间隔32个时钟周期。

3.2.3 测试程序

为了测试以上程序的正确性,特用vc6.0编写了一个计算机端的测试程序。该程序通过串口与jb8通信,以完成对b32 flash的读写和擦除。由于源代码较长,限于篇幅不在此列出。

评论