基于S3C4480X的大型LED显示系统设计

大型led显示系统已经广泛应用于各种室内外场合,但由于其多采用多机系统,提高了系统成本和软硬件设计复杂度。多机系统工作时,本质上相当于一个高总线宽度的计算机系统。其技术难点如下:

◆大型led显示屏上的像素数以万计,随着显示面积增大,电路结构随之增大。

本文引用地址://m.amcfsurvey.com/article/21261.htm◆为了保证一定的显示质量,帧频应在30帧/s以上。对于一个512×252的单色led屏,每秒的数据传输量至少为480 kb以上,对于彩屏及显示质量高的场合,数据传输量还将按整数倍增长。

◆当led屏位于室外时,上下位机通信可能在百米甚至千米以上,要求通信速度快且可靠。

鉴于上述前两个技术难点,为能够使用单cpu系统代替多机系统控制大型led显示系统,采取的应对策略如下:

◆大型的led屏由通用的显示模块组成,显示模块具有良好的通用性和可嵌入性。

◆使用16位并行总线数据传输方式,要显示相应位置的显示模块,模块上的列锁存单元能够准确选通,使横向级联的led显示模块能够被视为一段连续的存储单元。

◆使用s3c44box内部的dma控制器进行数据的传输和控制,节省了使用指令传输数据的cpu取指和译指时间以及使用指令传输数据附带的计数、比较、跳转等软件开销,从而能够在连续的读写操作中完成数据的传输,提高了数据传输的速度和效率。

1 硬件结构及原理

大型led显示系统一般分为主控板和显示驱动模块两部分。

1.1 显示模块

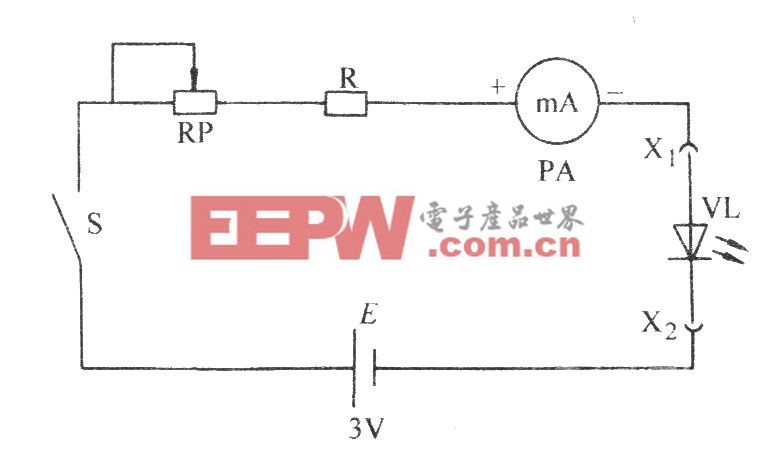

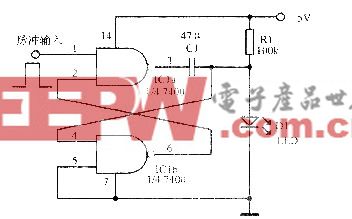

现今,大型led显示系统是利用人眼视觉特点采用逐行扫描和列驱动方式以节省硬件开支的,本系统采用1/16逐行扫描方式,所以整个大型led屏被分为16行同名行,显示模块原理图如图1所示。

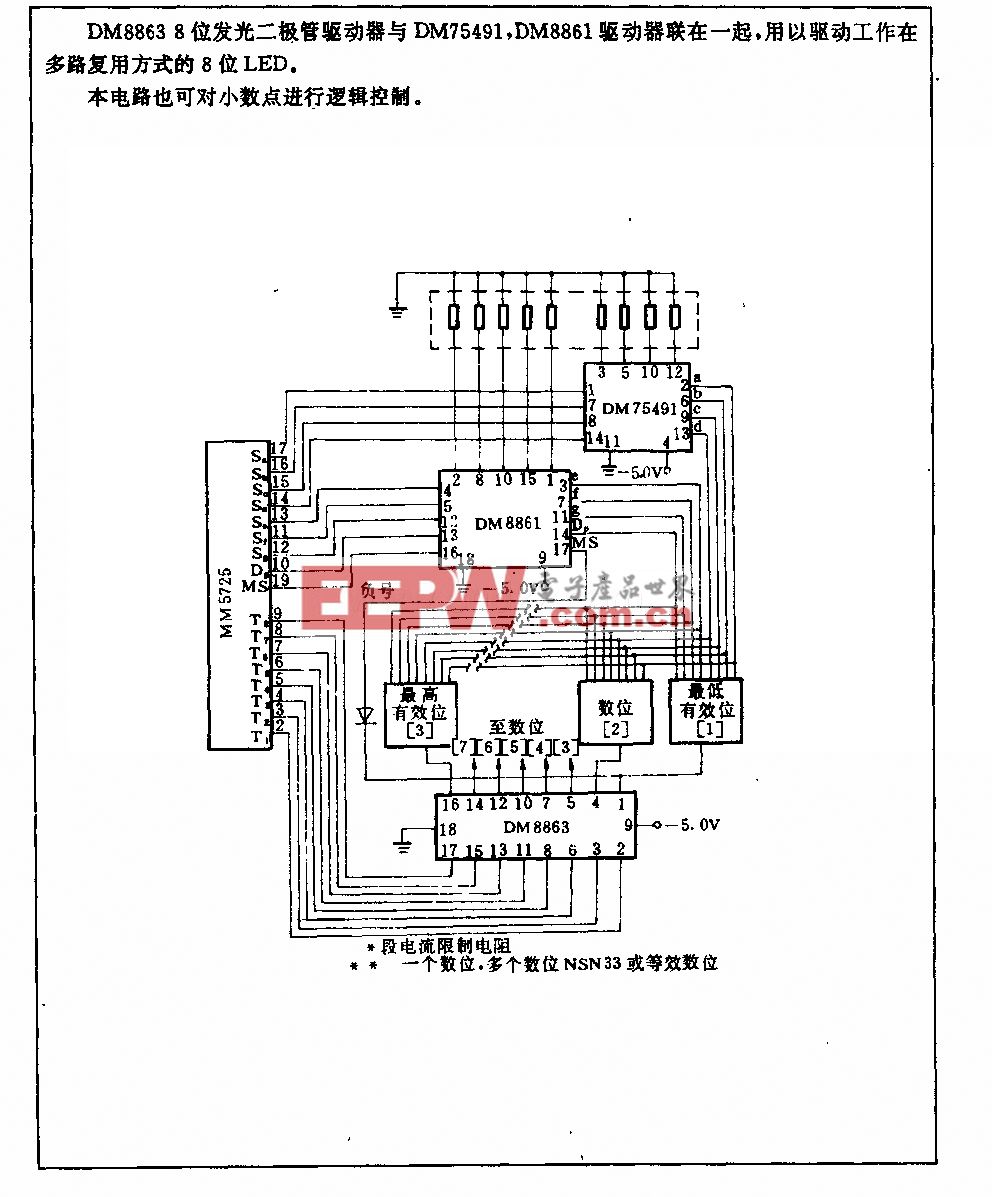

每个显示模块为1个64×32的小点阵屏,分为两部分,上下各16行,每部分有8组列数据锁存器。上下两部分复用1个4—16译码器u1,选通驱动1/16逐行扫描显示,并需要16组列驱动锁存器锁存列显示数据。采用并行总线数据传输方式时,需要1个4—16译码器u2选通使能列锁存器。在点阵刷新时,需要使用两级锁存器锁存列显示数据,否则会出现显示拖尾现象。本次正在显示的数据存在第二级锁存器中,主控板对屏端第一级锁存器写下一行要显示的数据进行列数据刷新,当下一行要显示的数据传输完毕后,一起锁存到第二级锁存器输出并选通驱动下一行显示。采用并行总线方式下二级锁存器仍比数据串行传输再转成并行输出的方案经济。

显示模块与模块之间横向级联时,运用错位级联的思想,使其具有良好的通用性和可嵌入性。如图1所示,选通线每到一级时就会错位一次并传到下一级,总是使第一根选通线blk_en0作第一级列锁存器译码器的使能控制线,这样n根选通线就能依次选通n级横向级联模块。这样就可以用相同的显示模块任意组合成横向级联的条屏。

运用错位级联思想,使横向级联的显示模块上的第一级锁存器的译码器u2能够依次选通,该译码器又能依次选通第一级列数据锁存器,这样横向级联屏上的第一级列数据锁存器就能看成一段连续的存储单元,这是使用dma并行数据传输控制的基础。

1.2 主控电路与led屏的接口设计

本显示系统选用基于arm7tdmi内核并带有内部dma控制器的s3c44box作主控制器,使其工作在arm状态,并使用16位总线。由于把led屏虚拟的视为一段连续的存储单元,故为其分配地址空间0x2000000~ox4000000。

主控电路与led屏接口应能实现以下功能:

◆选通任意位置的显示模块及该模块上的第一级列数据锁存器。将该位置要显示的点阵码准确锁存,并能在第一级列数据锁存器数据刷新后,将刷新数据锁存到第二级列数据锁存器并输出。

◆能控制选通驱动16行同名行中的一行进行逐行扫描显示。

◆实现主控芯片3.3 v到led屏5v的逻辑电平转换。

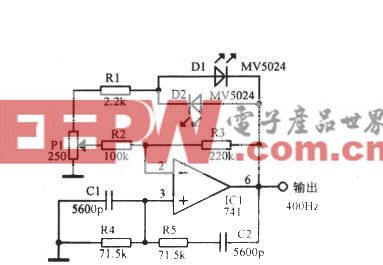

主控板与led屏接口电路原理图如图2所示。

一个大型led屏的结构可分为纵向级联和横向级联,这种结构类似于一个三维数组。假设一个三维数组led[i][j][k],其中:

i=0,1,2,…,m 表示led屏纵向级联级的序号。

j=0,1,2,…,n 表示led屏横向级联级的序号。

k=o,1,2,…,16 表示显示模块上16个第一级列数据锁存器的序号。

由于系统使用16位并行总线数据传输方式,并将led屏视为一段连续的存储单元,故使用a[4:1]作显示模块上选通第一级列数据锁存器译码器(图1中u2)的译码输入,即为三维数组的k变量;使用a[8:5]作选通横向级联显示模块的译码器(图2中u7)译码输入,即为三维数组的j变量;由于led屏要具有良好的灵活性,又由于采用dma传输数据要求点阵码存放顺序的技术要求,纵向级联级选通不满足使用地址总线译码选通的条件,所以使用s3c44box的pg[2:0]作纵向级联级选通译码器的译码输入,即三维数组的i变量。

由于地址和数据总线上的状态不断变化,所以在对led屏进行写操作时,地址和数据信号应进行锁存,主控板上分别使用u2、u3和u4锁存对led写操作时的地址和数据总线的状态。led屏分配首址为ox2000000,当对其进行写操作时,s3c44box的ngcsl和nwe脚会出现可编程控制时延的有效低电平。ngcsl经一个非门作u2、u3和u4的锁存使能控制信号,保证仅在对led屏访问时,地址和数据总线上的信号才被锁存。nwe经一个非门作屏端第一级列数据锁存器(图1中u3~u19)的锁存使能控制信号,保证只有当刷新数据稳定出现在列数据锁存其输入端时才被锁存。s3c44box的pci0作所有屏端第二级锁存器(图1中u20~u35)的锁存使能控制信号线;s3c44box的pc[3:o]作16行驱动译码器(图1中u1)的译码输入。由于数据传输时只需要主控板对led屏输出控制,不需要信号反馈,所以接口电路采用廉价的5v供电的hct电路芯片方案,就可满足主控芯片3.3v到led屏5v的逻辑电平转换。

在dma传输数据时,更关心的是dma的写操作,时序如图3所示。t1时刻dma写操作开始,地址和数据总线上出现led屏相应位置的地址和刷新数据;t2时刻ngcs1引脚出现有效低电平,地址和数据总线上的数据被锁存到u2~u4并输出;t3时刻nwe引脚出现有效低电平,u2~u4的输出数据被锁存到屏端第一级列数据锁存器并输出。这样主控制器就完成了一次列数据的刷新。

2 软件设计

2.1 led屏显示程序设计

由于使用了s3c4480x内部dma控制器进行数据的传输与控制,显示程序得到很大简化,程序流程如图4所示。点阵码的传输全由dma控制器完成,只需在启动dma数据传输前将点阵码的首址、led屏的首址及传输数据量的值分别赋给相应的控制字后,启动dma操作即可。完成所有本同名行点阵码传输后,将刷新的数据锁存到第二级列数据锁存器输出,并驱动本同名行显示。这样循环显示16行同名行后就完成了一帧点阵显示。

2.2 点阵排序

由于led显示模块的电路结构以及使用了16位并行总线和dma数据传输技术,在显示时点阵码的排放顺序,需要满足如下要求:

①16位并行总线一次数据传输,即一次dma写操作传输两个字节的点阵码,低位和高位字节分别传送到两相邻的纵向级联模块的同名行和同名列数据锁存器中,因此相邻的纵向级联模块的同名行和同名列点阵码应连续存放。

②由于显示模块的第一级列数据锁存器译码选通电路结构和dma数据传输要求,对同一显示模块的上下两部分的同名行点阵应按列数据锁存器的选通顺序依次连续存放。

③两相邻的纵向级联级的一系列横向级联级应按①和②原则进行点阵码排序。

④各纵向级联级依次按①、②、③原则进行点阵码排序。

⑤16行扫描显示方式下,一个大型led屏分为16行同名行,每一同名行按照①、②、③、④原则进行点阵排序。

以一个128×64的点阵屏第一行同名行的数据排序为例,如图5所示,第一行同名行的点阵码的存放顺序应依次为:a,b……z,a,b,……z……。

3 结 论

使用并行总线dma数据传输技术简化了led显示系统的软硬件设计,降低了系统成本,取得了很好的显示质量,在22.1184mhz的系统时钟下,512×256(8m2)单色点阵屏显示帧频达到250hz,平均120ns传送1个字节,达到了使用单cpu系统代替多机系统控制led显示系统的目的。但为了使上一代的显示驱动板仍能够使用,点阵码需要排序,显示时只能使用页面方式显示,这样在多页动态滚屏显示时需要大容量的存储器。对于512×256单色点阵屏需要数十兆的容量,使用32位arm7tdml内核先进控制器s3c44box和廉价的大容量sdram存储器可以使该问题得到很好的解决。若使用针对dma控制显示设计的显示驱动板显示时,点阵码就不需要排序,一片数百kb的sram就能满足系统要求了。

评论