基于FPGA 的ARM 并行总线研究与仿真

WE 为ARM输入到FPGA的写使能信号.CS 为ARM输入到FPGA的片选信号,FPGA没有被ARM选中时必须输出高阻态,以避免总线冲突.

2.2 FPGA 的双向总线设计

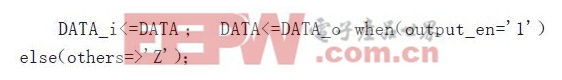

在FPGA 的并行总线设计中,如果顶层和底层的模块都要用到双向的IO 端口,则要遵守设计原则;否则不利于VHDL 程序的综合.双向IO 端口的设计原则是:只有顶层设计才能用INOUT类型的端口,在底层模块中应把顶层的INOUT 端口转化为独立的IN(输入).OUT(输出)端口并加上方向控制端口.顶层设计的VHDL 代码如下:

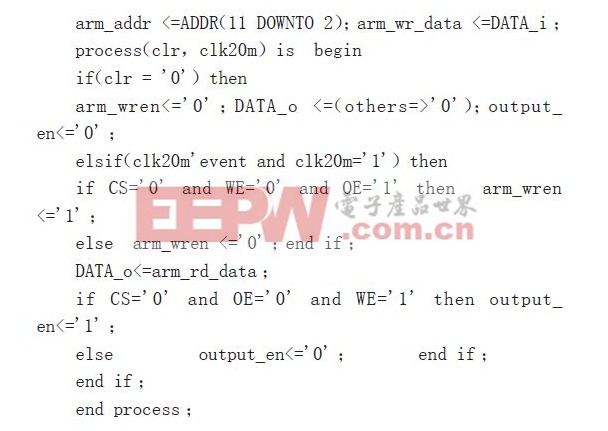

其中,DATA_i.DATA_o 和output_en 均为FPGA 内部的信号,在内部的各层次模块中,通过这三个信号就可以进行单向的IO 控制.这样,顶层设计中双向的DATA 端口转化为了内部单向的DATA_i(输入).DATA_o(输出)和output_en(输出使能).在内部各模块中,结合这三个信号以及ADDR.OE.WE.CS 等信号,则可方便地实现ARM 总线接口的功能.实现的VHDL 关键代码如下:

3 仿真结果分析

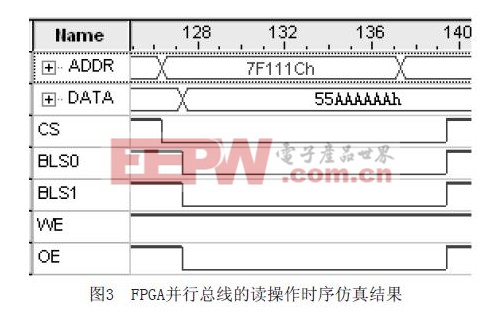

通过Quartus II 仿真工具,对FPGA并行总线进行时序仿真;仿真结果如图3 所示.根据ARM并行总线的读写时序图要求,从仿真结果可以看出FPGA 的总线接口设计满足了设计的要求.由于选用的FPGA 器件内部带有逻辑分析仪的功能模块,通过Quartus II 软件中的SignalTap II 逻辑分析工具,对FPGA的设计模块进行在线测试,发现总线时序了满足ARM 并行总线的要求,且工作稳定,从另一个角度验证了设计和仿真结果的正确性.

4 结论

由于FPGA 技术和ARM 技术应用越来越广泛,通过设计并行总线接口来实现两者之间的数据交换,可以较容易地解决快速传输数据的需求,因此设计满足系统要求的FPGA 并行总线显得尤为重要.本文设计的FPGA 的ARM 外部并行总线接口,满足了总线的时序要求,并在某航空机载雷达应答机中进行了应用,系统运行稳定,性能良好.以上的设计和仿真方法,对其他类似的设计也有一定的参考作用.

评论