C8051F单片机实验系统设计方案

2.3 SRAM模块

C8051F020内部有位于外部数据存储器空间的4 096字节的片上RAM,还有外部数据存储器接口EMIF,可用于访问片外存储器和存储器映射的I/O器件。外部数据存储器接口EMIF可配置到低I/O端口P0~P3,也可配置到高I/O端口P4~P7。而且,既可以配置为数据、地址复用方式,也可以配置为非复用方式。若要节省端口I/O,可采用数据、地址复用方式,能节省8根端口线,但是速度较慢,若要提高速度,则可

以采用非复用方式。

2.3.1 配置外部存储器接口的步骤

1)将EMIF选到低端口(P3~P0)或选到高端口(P7~P4)。

2)选择复用方式或非复用方式。

3)选择存储器模式(只用片内存储器、不带块选择的分片方式、带块选择的分片方式或只用片外存储器)。

4)设置与片外存储器或外设接口的时序。

5)选择所需要的相关端口的输出方式。

在本系统中考虑到(28051F020单片机的PO~P3口大部分为功能复用引脚,为使单片机的资源得到最大的开发,将单片机的高端I/O口,即P4~P7接入FPGA,并通过FPGA对RAM进行访问。将单片机配置为高端口(P4~P7)、地址/数据总线分时复用方式,FPGA控制RAM的片选、读/写等操作,其中注意FPGA、单片机、RAM的时序统一问题。

2.4 UART串口

UART是一种通用串行数据总线,该总线双向通信,可以实现全双工传输和接收。在嵌入式设计中,UART用来与PC进行通信,包括与监控调试器和其他器件,如EEPROM通信。

UART首先将并行数据转换成串行数据来发送。消息帧从一个低位起始位开始,后面是若干数据位,一个可用的奇偶校验位和一个高位停止位。接收器发现开始位时它就知道数据准备发送,并尝试与发送器时钟频率同步。在接收过程中,UART从消息帧中去掉起始位和结束位,对进来的字节进行奇偶校验,并将数据字节从串行转换成并行。UART也产生额外的信号来指示发送和接收的状态。例如,如果产生一个奇偶错误,UART就置位奇偶标志。

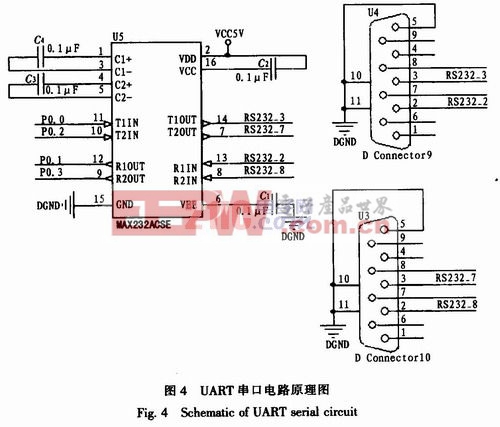

C805lF020单片机中有两个增强型串行口:UART0和UARTl。所谓增强型是指,这两个串口都具有帧错误检测和通信地址硬件识别功能。它们都可以工作在全双工异步方式或半双工同步方式,并且支持多处理器通信。开发板外扩两个增强型UART串口,实现单片机与PC机、单片机和单片机之间的通信。其电路连接如图4所示。

评论