串行RapidIO: 高性能嵌入式互连技术

在传统的基站中,DSP与ASIC或FPGA之间的互连一般用外部存储器接口(EMIF);DSP之间或DSP与主机之间一般用HPI或PCI互连。它们的主要缺点是:带宽小、信号线多、主从模式接口、不支持对等传输。另外,DSP不能直接进行背板传输。

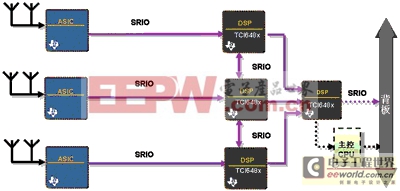

使用SRIO则可有效的解决这些问题,大大提高无线基站的互连性能。图8显示了一种无线基站基带互连框图。在这里,SRIO实现了大部分器件之间的互连,甚至可支持DSP进行直接背板传输。

图8 SRIO提高无线基站互连性能

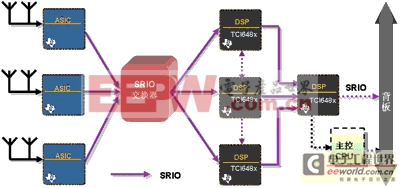

通过SRIO交换器件互连可以进一步提高基带处理的灵活性,图9显示了一种基带SRIO交换互连的框图。这种互连有利于实现先进的基带处理资源池架构,数据可被送到任何一个通过SRIO交换器互连的处理器中,从而达到各个处理器的负载均衡,更加有效的利用系统的整体处理能力。

图9 SRIO交换为无线基站基带处理提供更大的灵活性

综上所述,对嵌入式系统尤其是无线基础设施,串行RapidIO是最佳的互连技术。高达10Gb/s的带宽、低时延和低软件复杂度满足了飞速发展的通信技术对性能的苛刻需求;串行差分模拟信号技术满足了系统对引脚数量的限制,及对背板传输的需求;灵活的点对点对等互连、交换互连,和可选的 1.25G/ 2.5G/3.125G三种速度能满足多种不同应用的需求。

评论