基于FPGA的汽车ECU设计充分符合AUTOSAR和ISO 26262标准

在 RTE 之上,通过应用层,软件架构方式从分层变为以组件为基础。功能主要封装在软件组件 (SWC) 中。因此,完成AUTOSAR软件组件接口的标准化是支持各项功能跨不同车辆平台的ECU实现可扩展性和可移植性的中心环节。除复杂驱动程序外,AUTOSAR标准明确地规定了这些组件的 API 及特性。SWC 仅通过运行环境与其他模块(ECU间或内部)通信。

本文引用地址://m.amcfsurvey.com/article/221573.htm随着ECU不断集成越来越多的功能,FPGA器件成为了单核或多核MCU 的明智替代。通过从总体上把握AUTOSAR的不同层次,可以预见设计人员将这种架构部署在可编程逻辑中所能带来的优势。下文将更深入地介绍我们的设计如何实现基于定制静态硬件(基于闪存或SRAM 的FPGA技术)的解决方案,然后将这种方法延伸为为一种运行时可重配置的硬件实现方案(基于 SRAM 的部分可重配置FPGA)。

基于 FPGA 静态硬件的 ECU 设计

AUTOSAR 架构非常适合由 CPU、存储器和可编程逻辑组成的嵌入式系统。ECU 平台需要一个 CPU 或主机处理器来管理应用并处理分布在应用层的软件组件中的不同功能。同时,MCU 层和部分基础软件层可以在可编程逻辑结构中的硬件中综合。因此,除了能够实现与 CPU 相连的标准外设,其它定制外设和协处理器也能够在硬件中并存,并在软件中完全或部分地加以管理。

另外从功能安全的角度来看,专用协处理器或内核处理器也非常适用,因为用它们实现功能可让硬件从源头避免干扰,即便要求冗余性,也能给系统设计带来高灵活性。另外,居于中间的 RTE 层可以在分布于 FPGA 中的 RAM 模块中,或者在嵌入在器件逻辑单元中的触发器中以及外部存储器中综合。而且,RTE 信号接口经简单设计就能够同时进行读写操作(通过单端口存储器)或限制架构仅进行读操作或者写操作(通过配有两个独立读写端口的单个双端口存储器),以防范干扰,比如 AUTOSAR 所定义的彼此对应的发送器和接收器软件端口。

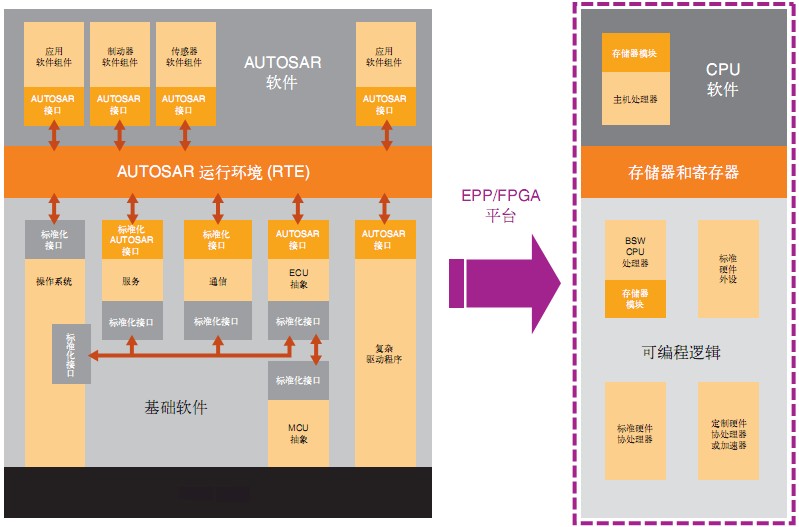

图2 将 AUTOSAR ECU 架构移植到 FPGA 平台上

建议将基于 MCU 的 AUTOSAR ECU 架构移植到可扩展处理平台 (EPP) 或者 FPGA 器件上,并在各层中确保清晰的系统分区,如图 2 所示。位于 RTE 层以下的有操作系统 (OS)、存储器协议栈、通信协议栈、I/O 协议栈等。位于 RTE 层以上的是软件组件,它们用于实现应用并通过 AUTOSAR 接口与 RTE 进行通信。

由于 AUTOSAR 架构内在的复杂性,需要功能强大的嵌入式计算平台才能进行部署。如今,典型的 ECU 设计基于运行在 MCU 平台上的 32 位单核处理器。但是单核越来越难以提供所需的全部计算能力。而使用多核 CPU 需要通过多处理器总线和仲裁机制共享程序/数据存储器,往往会导致高度复杂的解决方案,造成性能劣化。

作为这种方案的替代,我们提出了一种基于可编程逻辑的设计。这种设计只采用一个单核处理器来发挥主机 CPU 的作用,但配有更智能的外设、协处理器乃至从处理器。所有这些计算单元都可以在 FPGA 架构中例化为新的软核处理器,比如赛灵思 PicoBlazeTM 和 MicroBlazeTM,从 FPGA 的专用 RAM 模块运行自己的代码(各个软核处理器均分别配有专用程序存储器),此外,也可例化为定制的硬件加速器。两种方式的拓扑架构均由一个主机 CPU 和分担 部分CPU 任务的智能外设构成,从而可降低系统复杂性。这样,主机 CPU 负责管理软件中的整个应用层,而定制外设则负责管理 BSW 层,这两者以并行的方式彼此独立地自动运行。此外,这种外设设计的方法的优点还在于能够让主机 CPU 的软件执行更加线性化,即外设不会通过中断服务程序产生过多的请求 CPU 关注的中断。图 3 显示了这种系统的方框图及其对应为 FPGA 器件中综合的功能单元的组件细分情况。

图3 在 FPGA 中部署的汽车 ECU 方框图

FPGA 方法能够实现与多处理器平台相媲美的系统性能,且和单核处理器一样简单易用,这主要归功于采用了可与主机处理器并行处理的功能强大的、自动化定制协处理器。

这种方法能够实现与多处理器平台相媲美的系统性能,而且就软件开发和维护而言,和单核处理器一样简单易行。通过使用专用硬件构建可与主机处理器并行处理的功能更强大的自动化定制协处理器,就可实现这种最佳平衡。

从概念上来说,可以通过将这些系统架构用 RTE 接口划分为顶层和底层两个彼此独立的主要层次来要简化设计。顶层相当于 AUTOSAR 的应用层,由负责管理车辆中最终用户功能的软件组件构成。而底层则由硬件和基础软件乃至 RTE 链路构成。应用层从数值上来说,可代表约 90% 的车载高级功能,而且所有 RTE 以上的源代码都可重复利用。

同时,底层包含能够赋予顶层灵活性和多用性的全部功能。这即是说,底层可完成特定硬件平台上所有可重用功能的定制化。这样,顶层从本质上说是通过以有限状态机 (FSM) 形态实现的算法来实现对某些车辆负载、传感器和制动器的控制的一套软件功能。这些算法由 CPU 循环执行,并在操作系统控制的软件任务中调度。

底层还负责实现 CPU 连接的所有标准外设的驱动程序,例如 A/D 转换器、PWM 控制器、定时器或者存储器控制器,从而让顶层的抽象具备可行性。底层负责管理那些需要得到实时响应的事件。在这方面可编程逻辑能够起到一定的作用。其构想为:让主机 CPU 将应用当作一个简单的免受通常硬件造成的外部事件影响的软件功能序列来处理,但要定期读或写 RTE 信号,让 FSM 进行相应的调整。底层对硬件事件进行隐藏与管理,然后在 RTE 中对其进行预处理并更新特定信号,或作为结果,根据自身具体任务安排实时地执行特定的行动。

将定制硬件控制器连接至系统 CPU 可以最大限度地降低对共享资源的需求,只要这些控制器能够自动运行。从操作系统的角度来看,这样做有助于降低系统的复杂性(避免仲裁、时延、重试机制等)。

采用专用硬件的另一项优势在于可以更简便地实现一般在软件中通过多线程才能实现的某些功能,因为硬件较软件内在更具并行性。另外,这种灵活的硬件能够采用并行和流水线硬件设计,将算法计算强度高的部分进行硬连接,而不是采用冯·诺伊曼 (Von Neumann) 计算机所采用的序列软件方法,从而减少执行时间。

评论