基于Xilinx FPGA的千兆以太网控制器的开发

2)MAC接收模块

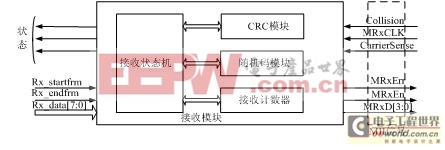

MAC接收模块结构如图10-33所示,负责数据帧的接收。当外部PHY将通信信道的串行数据转换为半字节长的并行数据并发送给接收模块后,接收模块会将这些半字节数据转换为字节数据,然后经过地址识别、CRC校验、长度判断等操作后,再通过主机接口写入外部存储器,并在主机接口模块的接收队列中记录帧的相关信息。此外,接收模块还负责前序码和CRC的移除。

图10-33 以太网MAC接收模块的结构示意图

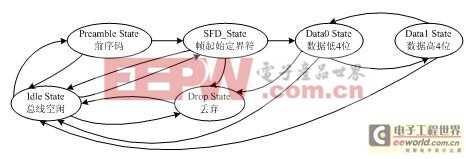

接收过程的接收状态机由Idle_State、Drop_State、Preamble_State、SFD_State、Data0_State、Data1_State等六个状态组成, 其状态转移图如图10-34所示。

图10-34 接收状态机的状态转移图

当接收模块检测到数据有效信号之后,,状态机将进入Preamble_State,并开始接收前序码。此后状态机进入SFD_State,接收一个字节的帧起始定界符,之后根据IFGcnt计数器的值进入不同的状态。如果IFGcnt所确定的时间大于96个比特时间,状态机将进入Data0状态以接收字节的低4位,然后是Data1状态,并接收字节的高4位,之后又回到Data0状态。状态机就一直在这两个状态之间循环,直到数据接收完毕(PHY清除MRxDV信号)后进入Idle,以重新等待接收新的数据;如果接收到帧起始定界符时,IFGcnt计数器所确定的时间小于96个比特时间,那么状态机将进入Drop_State状态,并一直维持该状态直到数据有效信号结束(PHY清除MRxDV信号)。之后,状态机再回到Idle等待接收新的数据。如果在接收前序码、帧起始定界符和数据期间,数据有效信号被清除,那么状态机将回到Idle。

3)MII管理模块

MII管理模块用于控制MAC与外部PHY之间的接口,用于对PHY进行配置并读取其状态信息。该接口由时钟信号MDC和双向数据信号MDIO组成。MII管理模块则由时钟生成模块、移位寄存器模块和输出控制模块三部分组成。

时钟生成模块可以根据系统时钟和系统设置中的分频系数来产生MII 管理模块的时钟信号MDC(10 Mbps速率时为2.5 MHz, 100 Mbps速率时为25 MHz)。移位寄存器模块既可用于对PHY的控制数据进行写入操作,也可用于对PHY的状态信息进行读出操作。写控制数据时,移位寄存器根据其他模块的控制信号将并行控制数据转换为串行数据;而在读状态信息时,移位寄存器则将PHY的串行数据转换为并行数据,MAC中的其他模块可将该并行数据写入适当的寄存器。

由于MDIO是双向信号,因此输出控制模块就用来决定MDIO是处于输入状态还是输出状态。当MDIO处于输出状态时,移位寄存器输出的串行控制数据在经过时钟同步后发送到PHY;当MDIO处于输入状态时,移位寄存器将数据线上的串行数据转换为并行数据

4)主机接口模块

主机接口是运行以太网的上层协议(如TCP/IP协议)与MAC控制器的接口。通过该接口,上层协议可以设置MAC的工作模式并读取MAC的状态信息。该接口还可用于上层协议与MAC之间的数据交换。

主机接口模块内有一组寄存器,可用于存储上层协议对MAC设置的参数以及MAC的状态信息。上层协议对MAC设置的参数包括接收超短帧的使能、添加填充码使能、发送超长帧的使能、添加CRC校验值使能、全双工模式或半双工模式、持超长延迟使能、混杂模式(Promiscuous)、接收广播帧使能、发送和接收使能、中断源和中断使能、帧间间隙的长度、最大帧和最小帧的长度、重试限制和冲突时间窗、MII地址和MII控制命令、接收和发送队列的长度以及本机MAC地址等。

上层协议通过MAC发送和接收数据的操作主要由主机接口模块内的两个队列来进行管理,这两个队列用于对等待发送的多个帧和接收到的多个帧进行排队。发送队列主要记录等待发送的帧的相关信息、发送该帧时对MAC的设置以及该帧发送完之后产生的状态信息。帧的相关信息包括帧的长度、帧在外部存储器中的地址、该帧是否准备好发送以及队列中是否还有其它帧等待发送;对MAC的设置则包括中断使能、填充使能、CRC使能;产生的状态信息包括成功发送之前的重试次数、由于达到重试限制而放弃发送、发送时产生的滞后冲突以及成功发送之前发生过的延迟。

接收队列主要对接收到的数据帧进行排队并记录每个接收到的帧信息。这些信息包括帧的长度、是控制帧还是普通数据帧、帧中包含无效符号、接收到的帧太长或太短、发生CRC错误、接收的过程中发生滞后冲突、帧是否接收完、队列中是否还有其它已接收到的帧以及帧存储在外部存储器中的地址等。同时队列中还有针对每个帧的设置位,用来设置是否在接收到帧时产生中断。发送队列和接收队列的长度都可以在控制寄存器中进行设置。

评论