一种基于EP2SGX系列FPGA的PCI接口设计

0 引 言

在现代雷达数据处理系统和其他应用系统中,传统的ISA、EISA等总线已逐渐无法适应高速数据传输的要求。而PCI局部总线以其高性能、低成本、使用方便和适应性等优点成为大多数系统的主流总线。其中常用的33 MHz、32位的PCI总线尖峰传输速率为132 MB/s。PCI总线接口相对其他总线接口来说是比较复杂的,它有着严格的同步时序要求,且为了实现即插即用和自动配置,PCI总线的配置空间有许多配置寄存器需要设置。本文在简要介绍PCI总线及其特点的基础上,介绍了如何利用FPGA设计PCI总线的接口电路,并给出了设计PCI总线接口时应注意的一些问题。

1 PCI总线与数据传输规范

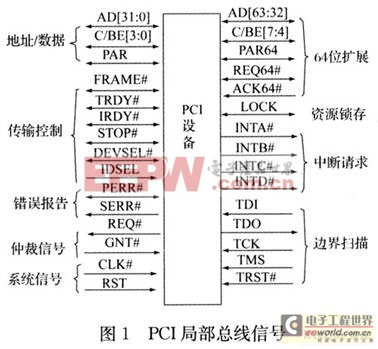

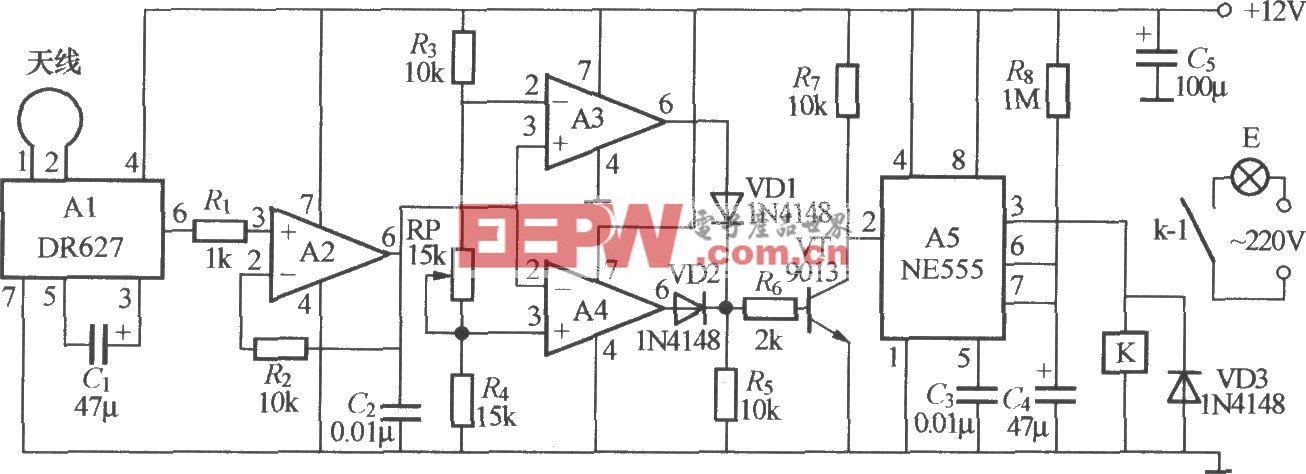

PCI总线信号可划分为如图1所示的几种类型。其中64位总线扩展信号、资源锁存信号和边界扫描信号是可选的。

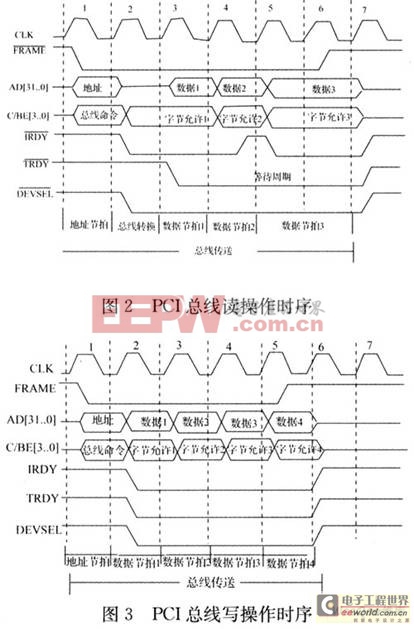

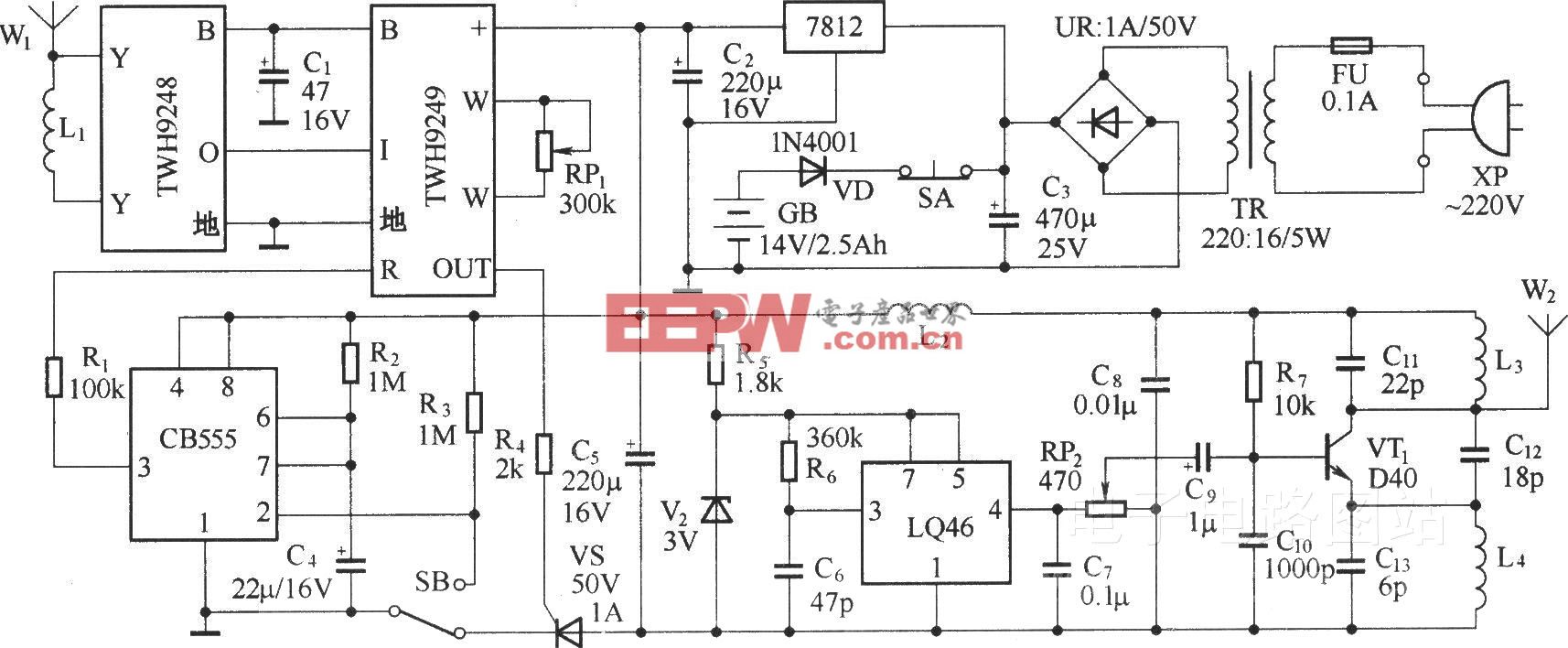

PCI总线上的数据传送是基于猝发传送的机制,一个猝发传送包括一个地址相和一个或多个数据相。基本的PCI传输由FRAME#、IRDY#和TRDY#信号控制。当数据有效时,数据资源需要无条件设置xRDY#信号(写操作为IRDY#,读操作为TRDY#)。接收方可在适当时间发出它的xRDY#信号。FRAME#信号有效后的第一个时钟上升沿是地址周期的开始,此时传送地址信息和总线命令。下一个时钟上升沿开始一个(或多个)数据周期,当IRDY#和TRDY#同时有效时,数据在主、从设备之间传送。在此期间,可由主设备或从设备分别利用IRDY#和TRDY#的无效而插入等待周期。PCI总线传输包含读、写和中止3个内容,图2和图3所示的时序图显示了PCI总线读、写操作的传输过程。

评论