高速流水线浮点加法器的FPGA实现

图3所示是其仿真的波形图。

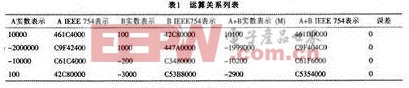

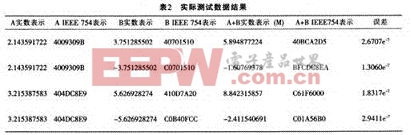

从图3可以看出表1所列的各种运算关系。表2所列为其实际的测试数据。

表中“A+B实数表示(M)”指Matlab计算的结果;“误差”指浮点处理器计算结果与Matlab计算结果之差。

综上所述,本工程设计的浮点加法器所得到的运算结果与Matlab结果的误差在10-7左右,可见其精度完全能够符合要求。

5 结束语

本工程设计完全符合IP核设计的规范流程,而且完成了Verilog HDL建模、功能仿真、综合、时序仿真等IP核设计的整个过程,电路功能正确。实际上,本系统在布局布线后,其系统的最高时钟频率可达80MHz。虽然使用浮点数会导致舍入误差,但这种误差很小,可以忽略。实践证明,本工程利用流水线结构,方便地实现了高速、连续、大数据量浮点数的加法运算,而且设计结构合理,性能优异,可以应用在高速信号处理系统中。

评论