便携式产品具有低功耗意识的FPGA设计方法

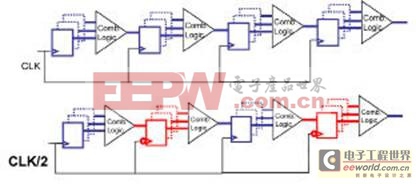

在降低时钟树的功耗方面,常用的方法有使用门控时钟,对常用的流水线时钟结构进行修改,尽量使用FPGA内部的全局时钟资源等。通过对常用的流水线时钟结构在RTL级进行修改,就像在图4中所看到的,做正反时钟沿间隔,这样时钟频率可以减慢一半,可以节省该时钟路径一半的功耗。同样可以通过人工对时钟域进行平面布局,来降低时钟树产生的功耗。这种方式对工程师的要求相对较高。Actel的设计师提供基于功耗驱动的布局布线策略。选择该策略,布局布线工具自动会在满足时序要求的情况下,尽可能的降低布局功耗。

图4 对常用的流水线时钟结构在RTL级做修改

要降低逻辑和走线的功耗,需要调整综合选项、了解算法/功能块的架构和功耗概况,通过减少信号的翻转来降低功耗。不同的综合选项和策略会对动态功耗有影响,基本上需要注意的是全局时序的设定以及set_max_fanout选项,以及是选用面积优先还是时序优先的综合策略。

通过对DesignWare和一些私有的加法器和不同频率下的功耗的评估,DesignWare下面的BK加法器在功耗方面是最友好的。针对同样5%到10%的速度降级,BK加法器和其他的私有加法器的核相比,可以减少10%到15%的面积和功耗。在选择乘法器的时候,必须要考虑乘法器的面积、功耗和速度。

计数器在设计中有不同的用法,有的用于计算事件发生的顺序或者用掉的时间,有的用于驱动类似于RAM的地址总线、数据总线、状态机的下一跳状态或者输出逻辑,有的用于当输出的值达到不同的解码值时做不同的设定的处理。根据不同的用途可以考虑用二进制顺序计数、格雷码计数、环形计数的实现方法。如果计数器只是用于产生一些标记,建议采用二进制的实现方式;如果计数器用于驱动一个大的负载总线,建议用格雷码计数器;如果多个计数器的值需要被解码,环形计数器是最佳选择(译码逻辑是最小的)。

通过降低逻辑的翻转率来降低动态功耗

首先在设计中,需要尽量避免不必要的翻转,可以通过下面几个步骤来实现这一目标:首先分析哪些逻辑的翻转是不必要的,随后对不必要的逻辑翻转的传播进行限制,展开逻辑翻转的时间。

减少逻辑可能产生的毛刺,先标识出翻转率高的网络以及它们的驱动,然后对驱动单元输入的最坏时序情况做评估,随后将毛刺的源往前调或往后调,然后对驱动单元的输入的最坏时序情况做评估,最后在驱动的逻辑后面插入一级触发器,根据先前的评估情况来决定用路径上其他时序元件的相同时钟沿或者相反的时钟沿来驱动触发器。即使是在单周期路径上面,如果有足够的slack来增加一个与门以及相关走线,那么就可以用与门的另外一个输入(毛刺源驱动寄存器)的反相时钟沿,从而减少毛刺。在某些情况下,可以通过伸展反转时间来降低毛刺的峰值功耗。

建议设计者要了解最终系统的运行模式,以及每种模式下系统的功耗概况。如果系统处于睡眠模式或者关闭模式的时间较长,需要观察浪涌电流和编程电流的影响,并处理好静态功耗。需要检查设计的动态功耗概况,找出功耗的主要瓶颈,根据概括表(图5~图8)找出最好的解决方法。

图5 RAM 动态功耗概括表

评论