H.264/AVC中量化的Verilog方法介绍及实现

具体量化过程的运算为:

![]()

式中:“》”为右移运算,右移1次完成整数除以2;sign()为符号函数;f为偏移量。f的作用是改善恢复图像的视觉效果,如对帧内预测图像块f取2qbits/3;对帧间预测图像块厂取2qbits/6。

3具体实现

在该文中,用Verilog语言实现H.264的量化;运用Modelsim进行仿真;用QuartusⅡ进行综合。

根据Verilog编程,Modelsim仿真如图1所示。

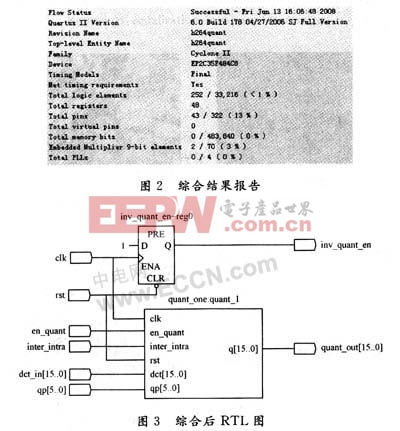

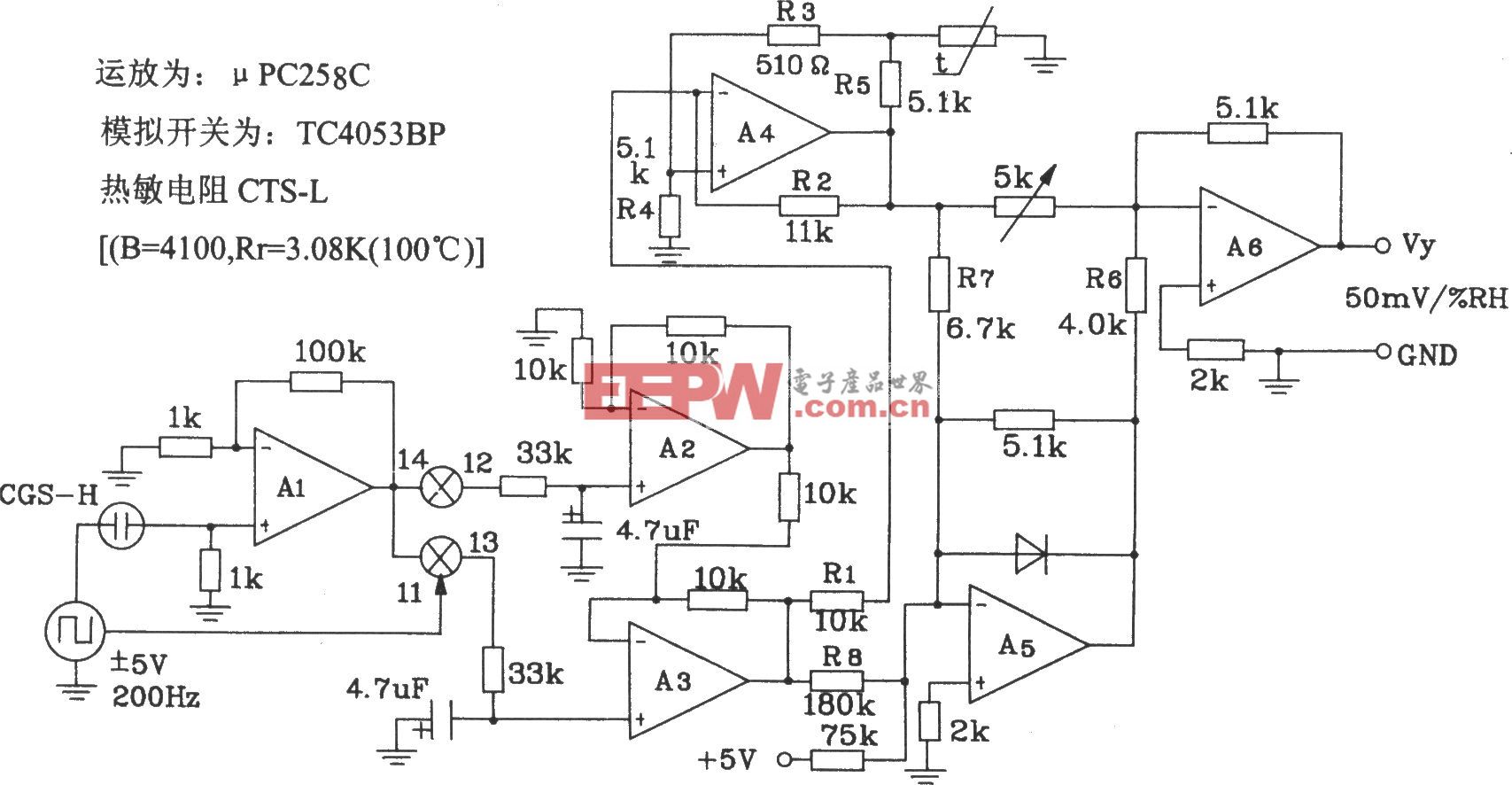

输入的矩阵是[140,-1,-6,7,-19,-39,7,-92,22,17,8,31,-27,-32,-59,-21],最后量化的结果为[17,0,-1,0,-1,-2,0,-5,3,1,1,2,-2,-1,-5,-1]。由此可知,这与Iain E.G.Richardson给出的结果相符合。所用的开发板是红色飓风第三代开发板,FPGA芯片是Altra EP2C35F484C8。从综合后的报告可以看出,消耗的资源不到1%,如图2所示。综合后的RTL图如图3所示。

4结 语

介绍了H.264的量化算法,并用Modelsim进行了仿真,结果与理论完全一致。分析了在FPGA开发板上的资源的消耗。由此可知,完全可以用FPGA实现H.264的量化。

评论