利用FPGA简化3GPP-LTE基带开发

基带处理信号通道是设计人员面临的最大挑战,但同时,它也为实现基站收发信台的创新提供了绝佳机会。因此,目前其已然成为OEM厂商实现产品差异化的关键。随着人们逐步认识到,许多针对之前2G和3G系统的技术将无法满足3GPP LTE,即第4代无线技术的性能和延迟要求,基带架构设计领域的竞争也开始愈演愈烈。

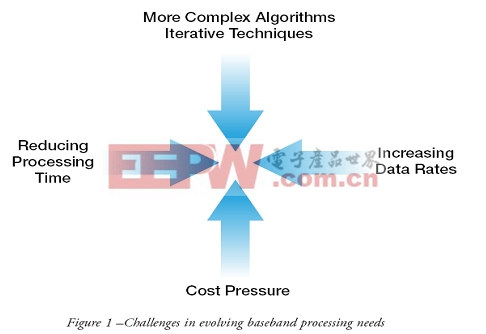

处理通道不仅需要比以往强大得多的处理能力,而且所有功能必须在更短的时间内完成。要想解决系统架构师所面临的一系列挑战,就要开发一个系统,来满足运营商积极的投资和运营成本削减目标。图1显示了基带处理系统设计面临的主要压力。

F1: 不断演进的基带处理需求带来的挑战

基于FPGA的解决方案可以满足上述要求,同时还能避免常见的性能问题和瓶颈。很多公司正在实施类似计划,如赛灵思最新推出的LTE上行链路通道解码器和LTE下行链路通道编码器LogiCORE,希望通过在单一IP解决方案中纳入多种关键的Layer-1功能,来消除FPGA普及道路上的种种障碍。

硅技术的进步是无线通信技术能够取得成功的关键,因为它可以将甚至更复杂的算法技巧从实验室带到实际产品中得以推广。例如3G网络中Turbo迭代码纠错技术,在10年内完成了从最初发现到商业化推广的整个过程。创新步伐始终都在持续加快,最为引人注目的是通过各种MIMO天线技术将空间维度(spatial dimension)概念应用到无线通信网络中。

但是,随着4G空中接口的出现,压力不断增加,以至于传统的以DSP为中心的可编程通道卡架构难以应对。FPGA和DSP之间的传统分割遭遇了性能瓶颈,这种制约的影响很大,因为二者之间需要传输的数据量非常大。

那么,我们如何才能消除类似瓶颈?关键在于简化Layer-1系统架构,并消除芯片间所有不必要的数据传输。这样的简化流程会引发一些与基于DSP的架构可扩展性有关的问题。设计人员需要IP、软件和技术支持等更强大的组合,来帮助他们完成向Layer-1系统架构的转变,在这其中,多数功能都在可编程的硬件环境中实现而非DSP。

评论