利用低成本FPGA设计下一代游戏控制台

基于平台的游戏控制台设计考虑因素

FPGA可以帮助系统设计者尽可能地节约成本并提供最大的灵活性,这是由基于平台方法通过提供以下设计方针来实现的。

需求和模型可随着区域而变化:针对多个标准和格式提供可编程支持能加快产品上市时间;低成本和可靠的设计:集成全部的系统I/O接口、控制逻辑和调试功能,以支持连接至HDD和内部存储器的ASIC/ASSP芯片组的桥接功能,定制的用户接口逻辑可降低在新产品中的风险;在最终测试期间和现场的安全编程能够实现对多种标准的支持、协处理算法的增量升级以及易于对新功能进行测试。

带有嵌入式DSP解决方案的FPGA

在选择面向平台的可编程器件时,通常需考虑三种电路要求:面向协处理功能的嵌入式DSP的功能和性能、查找表(LUT)以及RAM块(EBR),这种协处理功能利用并行方法,针对具体应用以最优成本对功能和性能进行裁剪。低电压差分信号(LVDS)和串行解串器(SERDES)可支持高速芯片至芯片接口,如HyperTransport、PCI Express或串行RapidIO。能够安全地保护知识产权。

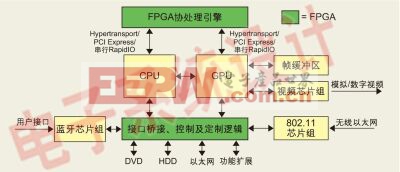

图2显示了一个满足这些要求的FPGA解决方案。FPGA被连接到主CPU、图像处理芯片、用户接口和诸如无线以太网的其它关键ASSP。FPGA模块执行协处理功能和硬件加速,并具有实现未来功能所必需的定制逻辑,这些功能是针对用户接口或控制台的其它部分。

图2:可重构FPGA能支持多个I/O标准、高速接口以及针对硬件加速的协处理算法。

DSP协处理和硬件加速

尽管低成本FPGA通常工作在小于300MHz的系统时钟频率下,但通过并行地执行串行功能仍然可实现很高的DSP吞吐量(63,000MMAC)。例如,某个应用要求具有100MS/s采样率的32抽头FIR滤波器,那么需要带有4个乘法器的通用DSP处理器以800MHz计算乘累加。具有32个乘法器的FPGA能够在100MHz实现相同的滤波器。

与乘法器一样,能够灵活地利用FPGA的并行特性有益于存储器访问。片上分布式存储器可用来构建小容量高性能临时存储器,而片上嵌入式存储块可用来构建大容量高性能存储器。DDR DRAM等片外存储器则可以提供大容量、高性能存储器。

评论