表面贴器件PCB占位的设计经验和指南

您正在设计一个包含IC或其它元件的PCB,而您的PCB布局软件缺乏占位设计功能吗?请不要担心,虽然不能获得用于生产的优化设计,但您仍然能够快速而方便地创建一个适用于原型的PCB布局封装元件占位。

只要从数据页获得元件封装的机械图纸,下面的指南就帮助您快速地设计出诸如铜层占位、焊料掩模孔、焊料粘结剂模版孔这样一些所需要的PCB孔,尽管不适用于生产,但这些指南将帮助您的原型设计顺利进入测试实验。

有些工程师感叹,过去那种能够在实验室中快速地对电路构想进行测试和验证的“面包板”原型时代,已经一去不复返。生育高峰时期出生的工程师们尚在深深地怀念过去晚上在餐巾纸上画好电路草图、明天就在实验室用电线搭成电路、在工作台上就可以通过验证实际工作情况和观察波形来试验设计思想的时光。不过,这并不意味着他们习惯于一些乱七八糟的接线。即使在面包板问世以前,设计人员也是非常仔细地考虑元件的布置和信号线的走向问题以避免串扰、飘移电感和电容对电路造成负面影响。

无论如何,今天精巧的SOIC和QFN封装技术从根本上对手工焊接造成了困难,信号带宽也提高到无法与点对点“鼠穴”状接线兼容。另外特别是像ASIC这样的许多半导体元件只有表面贴装形式。这样,在设计一个SOIC时一般都不会选择双列封装的原型。即使有便于手工焊接的封装元件,在信号传播和相位关系方面,原型与生产设计的高密度布局也可能存在差别。

快速将PCB转换为原型

在过去制作PCB时,要将胶带和粘结占位木模按放大了2倍或4倍的版图人工粘贴在一片聚脂薄膜上(以便于照相缩版处理和制作出1:1的接触式感光胶片)。很早以前,精心开发的PCB CAD布局软件已经取代了过去这种单调乏味的、通过手工“掩膜”来制作PCB艺术品的工作。

现在,工程师可以依靠软件自动进行布线设计的调试过程,最新的CAD软件提供了直观的图形用户界面,而且还支持从相关的原理图(原理俘获)程序中导入元件和接线信息(即网表信息)。

如果这些原理捕获/PCB布局软件包与基于互联网的快速转换PCB原型库结合起来,就可以获得过去的那种便捷的面包板功能,仍然可以设计出接近于最终设计的原型。目前有许多比一次工作午餐还要便宜的软件包可供选择,学习掌握这些软件也只需要几小时的时间。许多软件附带有包含数千个公用元件的库,因此不需要实地选择元件并将它们布置在实验板上。

按如下5个步骤使用CAD软件可以快速而简便地制作出 一个原型:

一个原型:

1.首先使用原理捕获软件绘出电路,从库中选择元件,将引线和总线连接起来。

2.将捕获的电路原理导入到PCB布局软件,移动元件封装直到获得紊乱最小的元件座,然后进行布线,软件即可以生成一个CAM文件。

3.在线订购板件和焊接模板,上载CAM文件。

4.一旦接受所订购的板件,就可以制做印刷版。

5.装配原型。

由于有了PCB后就可以进行装配,所以前端原理捕获和电路布局就比制作过程需要更多的时间。实际上,采用焊接模版将焊料印在PCB上,装配就成了一件将元件放置在相应的占位,然后将装配好元件的电路板放进回流炉这样一件简单的工作(注意:一个专用的“烘烤炉”更适合于回流工作)。

原型设计中的问题?

在设计中您可能会发现库中没有您所需要的元件,但这个问题确实是一个非常普遍的问题(在只包含一般元件的PCB布局软件的元件库中就可能没有ASIC或新型器件或特殊器件)。在这种情况下,电路设计师或原型师必须为软件包的元件库自己创建相应的器件。

这项工作不仅包括PCB铜层占位、也包括焊接模版、焊接掩膜、丝网图例、元件位置和方向的设计。不过,一个典型的双面板会包括几个与每个元件有关的特殊层,不过不需要担心,如果采用逐步逼近的方法,创建库中没有的器件也不是一件令人退缩的困难事情。

双层板的一般要求

一般设计工作先从确定PCB元件占位的层数开始。在电路板的上面(“元件侧”)必不可少的布线层是铜层、焊接掩膜层、焊接模版层和丝网图例层,另外还有元件质心/原点层和文档层可选。

当然,铜层是提供器件焊接连接面的主要板层,焊接掩膜层可以防止液态的光学成像(LPI)焊接掩膜漆料覆盖焊接区域,模版层(油膏层)为用来将焊料“印刷”在铜层的不锈钢模版提供光孔图案,丝网图例层包含元件轮廓和方向的工艺图、器件ID和元件号。

原点(元件质心层)提供贴装设备所需要的信息,而文档层一般用来给出器件的概略说明,这两层都不会出现在实际电路板上。

器件的数据册中可能会包含或不包含针对具体封装的推荐占位图纸(如果包含这样的图纸,则在铜层简单地再现同样大小和样式的焊盘即可),但在其它出版物中也可以找到这些信息。例如,Freescale应用笔记AN2409中就提供了整个微距SOIC封装系列器件的焊盘尺寸。

在使用PCB布局软件逐步创建一个表面贴装焊盘的过程中,我们假设没有提供占位图纸。在这个练习中,我们以四方扁平无引线(PQFN)封装电源器件做为例子。

在Freescale公司的应用笔记AN2467中是这样定义这个先进的封装电源器件的:“PQFN是一种表面贴装塑性封装器件,引线盘位于该封装元件的底面。所有PQFN封装器件都设计有单个裸露芯片安装盘(标记)或多个裸露芯片安装盘,这取决于器件要求和目标应用。工业标准化委员会JEDEC已经注册了一个标志符MO251用以描述单个裸露盘PQFN封装。”在本例中所使用的器件数据册是MC33922/MC3492 4.0A双电源H桥。

铜层

要布置占位,首先打开PCB布局软件的库编辑器,在现有库中创建一个新的元件或为新元件创建一个新库,然后选择菜单创建一个新的封装元件,这点上大多数PCB布局软件包都可以提供2D分层制图屏幕。

现在将您的注意力转到数据册第19页#146902组29端子PAFN塑性封装的封装尺寸图(图1)。注意尺寸单位,将制图屏幕上的栅格设置到同样的单位(在本例中为毫米)。另外也注意封装轮廓的尺寸(10×10mm),用后面就要删除的临时线以绘图原点为中心绘制此轮廓,做为参考。

下一步是获得与PCB紧密接触的端子(引线)部分的尺寸,这是因为需要根据这些端子的尺寸来确定相应铜层焊盘的尺寸。在本例中,有四种不同尺寸的端子:其中16个端子长1.525 mm(标称)、宽0.565 mm(标称);8个端子长0.775 mm(标称)、宽0.565 mm(标称);4个端子长1.005 mm(标称)、宽0.565 mm(标称);一个端子(裸露的散热盘)长达9.4 mm(标称)、宽6 mm(标称),每个角都带有一个半径近1mm的固定点。

最后,注意元件外围引脚中心与引脚中心之间的间距,在引脚中间部分标称间距为0.8 mm。现在已经获得了绘制元件占位所需要的基本尺寸数据。我们给出的第一条指南是:

指南1:对于间距非常小的精细间距端子,创建一个其宽度略微小于引线/端子宽度的焊盘,向外拉长一些,使其长度大于引线/端子长度。

这样可在端子之间保持一个最小的焊接掩膜,在端子的头部提供一个明显的焊接片,对于产品设计,这个焊盘宽度可以再宽一些。但是,对于原型设计,必须保证将端子之间搭接的危险减小到最低限度,这样才能避免将时间浪费因焊料过多引起短路故障的排除上(此情形类似于手工制版涂敷焊料的过程) 。

对于16个1.525×0.565mm的端子,可按1.675×0.515 mm的PCB焊盘尺寸对待,这样就可以用PCB布局软件来创建这种尺寸规格的焊盘(例如,选择“change”,再选择“Smd”,然后输入1.675 x 0.515即可)。特殊尺寸的焊盘也可以这样处理(尺寸较大的散热盘除外,将在后面介绍有关方法)。

指南2:以俯视PCB铜层的视角创建占位。

这意味着在图上引脚1的位置和方向应该与通过X射线向下透视铜层时所看到的位置和方向一样。许多PCB布局软件在创建焊盘会依次编号,确认第1个焊盘设置在引脚1的位置,然后以俯视角度依次布置其它焊盘。

为布置这些焊盘,需要临时改变网格间距,使其等于标称引脚中心之间间距的一半(在本例中为0.4 mm),按照元件封装端子的方向布置焊盘。注意焊盘的位置使其长度超出封装周界大约0.15 mm,然后继续按引脚顺序布置焊盘,在布置到临近边时,牢记必要时改变焊盘尺寸,重新调整引脚引脚基线间距(图2)。

|

指南3:将裸露的散热焊盘(如果必要)作为一个单独的、特殊的端子焊盘放在端子序列的最后进行布置。散热焊盘的尺寸应略小于元件的裸露散热标记的相应尺寸(比如长宽各小0.1 mm)。

经过专门设计SOIC和QFN功率元件有一个允许直接从IC底部向PCB散热的裸露散热标记,为保证有效散热,PCB上必须有一个带有散热孔的裸露焊盘区域以冷却更大面积的铜层(PCB低部及(或)多层PCB的内层),裸露的焊盘必须创建成一个不规则的多边形。

注意选择合适的线条宽度以绘制细节部分,但线条也不要过细,以免耗费大量的CAM工具处理时间。(记住将多边形用同样宽度的线条进行填充)。用户可以使用某些元件库对细小复杂的裸露焊盘进行简化,但必须注意在焊盘周围保持至少0.2 mm的最小空隙(图3)。

|

继续工作前,不要忘记删除铜层的临时参考线。设计铜层的裸露焊盘并不困难,但要设计焊料掩膜层(阻焊层)和焊料模版层的裸露焊盘还是需要一些技巧的。

焊接掩膜层

完成了铜层的设计后,下一步自然是创建焊料掩膜层(阻焊层)的工艺图。焊料掩膜包括电路板上那些不需要粘附着焊料的区域,这样焊接掩膜由焊接掩膜区域内的光孔组成,在有光孔的地方铜层裸露出来以便于焊接。

在第一种情况下,根据焊接掩膜来考虑焊盘的设计(SMD),这就是说掩膜决定可焊接的铜层区域,这是因为掩膜层覆盖铜层。由于掩膜创造了一个双倍依附于PCB基板的踪迹,这样即使在多次脱焊和重焊的情况下也不可能剥离,所以有利于原型设计,另外还可以有效保护免于焊接搭接和其它原型短路的危害。

不过,在产品设计中那些小尺寸端子的SMD焊盘是不受欢迎的。这是因为铜层焊盘的顶部焊接掩膜边缘会在焊接点产生应力点,在经受长期的周期性温度变化时会产生裂缝。鉴于这个原因,在产品设计中,掩膜光孔应大于焊盘尺寸,以使铜层焊盘周边有一个大约0.065 mm的外围区域,这种情况叫做非焊接掩膜决定焊盘(NSMD)。

指南4:原型设计中对于间距非常精细的引线采用SMD焊盘,而在生产设计中采用NSMD焊盘。在这个PCB原型设计的示例中应该使用SMD技术。最容易的方法就是将焊接掩膜光孔设置得与铜层焊盘尺寸一样大,如果所使用的PCB布局软件自动产生掩膜,则设置其最大尺寸,使其等于焊盘自身的尺寸(即不增大尺寸),另外通过放大并将分辨率设置到最高也能很容易地在铜层创建略微小于焊盘的四方形区域。然后通过观察和跟踪铜层焊盘的内轮廓绘制掩膜层光孔。

一旦创建了不同的焊盘四方形,就可以简单地将它们复制粘贴到焊盘内。尺寸大的裸露焊盘可以作为整体复制/剪切粘贴到掩膜层。图4给出了PCB布局软件中带有铜层和掩膜层的占位边角的放大视图。注意其中的正方形焊盘有一个略小于焊盘(以灰色表示)掩膜孔眼(以黄色表示),因此这个焊盘就是焊接掩膜决定焊盘。

|

焊接模版:下一步是创建确定焊接模版层的工艺图。这个模版在丝网印刷过程中用来将焊料粘结剂准确地涂敷到PCB的焊盘上。模版紧密地贴在PCB表面,过孔的图案应该完全与铜点的图案对齐。然后用一个刚形的橡胶滚轴碾压,迫使焊料粘结剂透过模版涂到PCB上,即使采用手工方式,每分钟也可以用焊接粘结剂“印好”数张电路板,以备下一步装配元件。

涂敷到电路板上焊接粘结剂量取决于两个因素—模版孔眼面积和模版的厚度。采用激光切割方法可以在切割PCB的同时切割出适用于原型的不锈钢模版,也可以通过互联网公司获得。模版的一般厚度是6 mils(0.006 英寸),具有足够的粗糙度,可在手工制作过程中反复使用。这里假设在模版层设计中也采用同样的厚度。

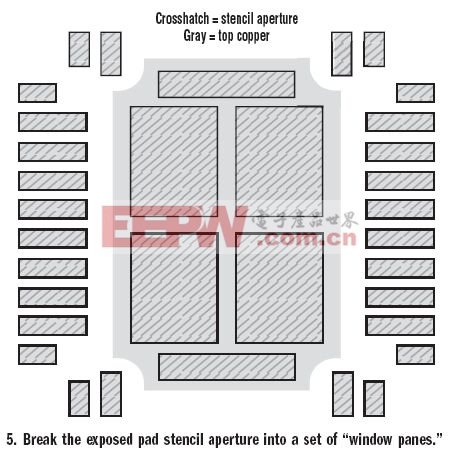

指南5:除那些裸露的散热焊盘或其它大尺寸光孔外,所有引脚/端子焊盘都采用1:1的焊接模版孔眼比。对于大尺寸的光孔(3×3 mm或更大)将其周边收缩0.25 mm以便在大尺寸焊盘与周围引脚/端子焊盘之间留下足够的间隙,并将大尺寸光孔分解成多个“窗格”。

如果将PCB布局软件从“cream(焊膏)”重新设置到“on”则可以自动完成上述任务,为每个端子焊盘的模版层创建一个1:1的光孔,在使用6mil厚模版的情况下,非常适合于精细间距和标准间距引线。

不过,对于裸露焊盘多边形,需要手工来创建版图。首先切换到铜层(这样可以观察到此多边形)和模版层(在这两层将绘制光孔),然后选择PCB布局软件的正方形功能,在正方形区域内创建一组窗格孔(确认您将这些正方形设置在模版层上)。图5所示为覆盖在铜层版图上已完成设计的模版孔眼。

|

注意从多边形边界、特别是从边角(向内)分离裸露焊盘模版孔眼的方式,这可以减少焊料过多和焊接短路的可能性。

丝网层

丝网层可以携带希望出现在PCB上的人机界面信息,它对电路功能没有任何作用,但对于原型是很重要的,有助于在装配电路板时确定元件的方向和位置,并能够对测试和调试提供协助。

按照惯例,丝网层由元件名称层、位置层和数值层组成,元件名称层提供元件ID,例如U1、R1、C5和Q。数值层包含与元件有关的参数,例如1k 或0.01 F。而位置层包含元件的轮廓和方向信息,我们认为提供位于顶层的位置层是最起码的要求。

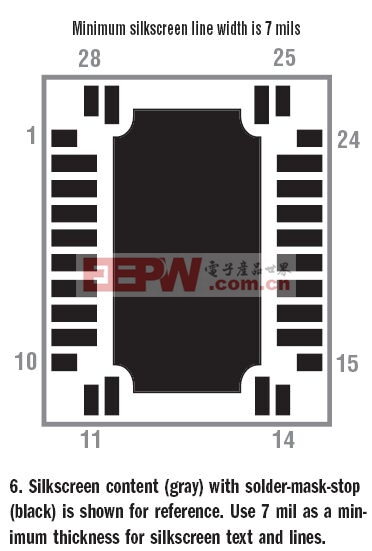

指南6:采用最小7mil(0.007in.)的丝网线宽。改变字体类型到“vector”,并根据需要调整比例和尺寸以创建可读的字母和数字。

不要在每个引脚旁边设置数字,应该在SOIC的引脚1上设置标签。对于QFN封装元件,在每个引脚的角上标注数字是有益的。在顶层的位置层绘图时保持上层的掩膜层(阻焊层)视图处于可见状态,主要不要使丝网数字/字母/线条与焊料掩膜孔过于接近,否则墨水将会洇到已作好的PCB焊接掩膜下陷部位。

保持最小的线条宽度,调整字体比例和尺寸以获得便于阅读的文本,在元件周围设置一个轮廓也是有好处的。图6给出了示例器件的最基本的丝网信息,同时也给出了掩膜层做为参考。

|

循这些步骤,就可以创建任何PCB布局元件占位,虽然没有针对生产进行优化,但对于原型应用而言却是鲁棒的,特别是可以取代适用于“餐巾纸草图”的原理捕获软件,迅速用焊接模版代替手工配线面包板,保持快速的概念实验循环,支持工程师的创新活动。

评论