基于FPGA的TDICCD8091 驱动时序电路设计

3.2 时序仿真结果

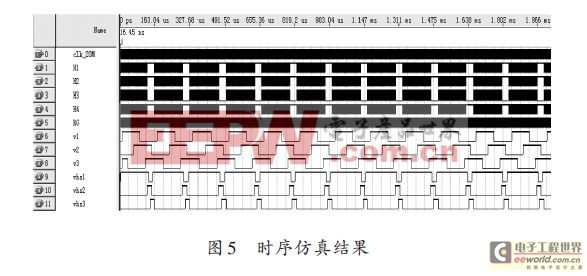

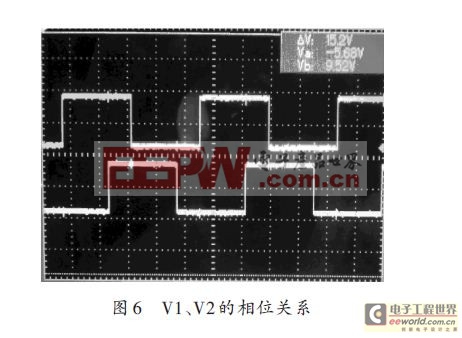

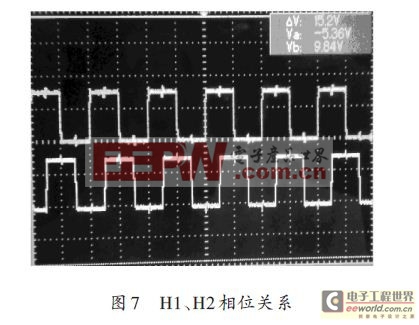

时序设计采用Altera公司的Quartus Ⅱ作为开发平台,EP3C25Q240为硬件平台。总的时序仿真结果如图5所示,结果表明所有仿真信号满足2.2节中的信号要求;图6为FPGA上测得V1、V2的相位关系,图7为FPGA上测得H1、H2相位关系,结果表明相位关系正确,能够保证每个时刻至少有一个高电平和一个低电平,保证像元电荷的正常读出。

4 结语

时序在硬件电路中成功驱动了TDICCD8091工作,验证了软硬件的正确性和准确性。程序设计利用同步时钟控制全局电路的思想,避免竞争与冒险,提高了程序的可靠性;采用模块化设计思想提高程序的可重用性、可测试性、可读性及可维护性;状态机的设计方法提高了程序运行的稳定性。

评论