使用创新性逻辑技术降低移动设计功耗

低ICCT技术有利于节能

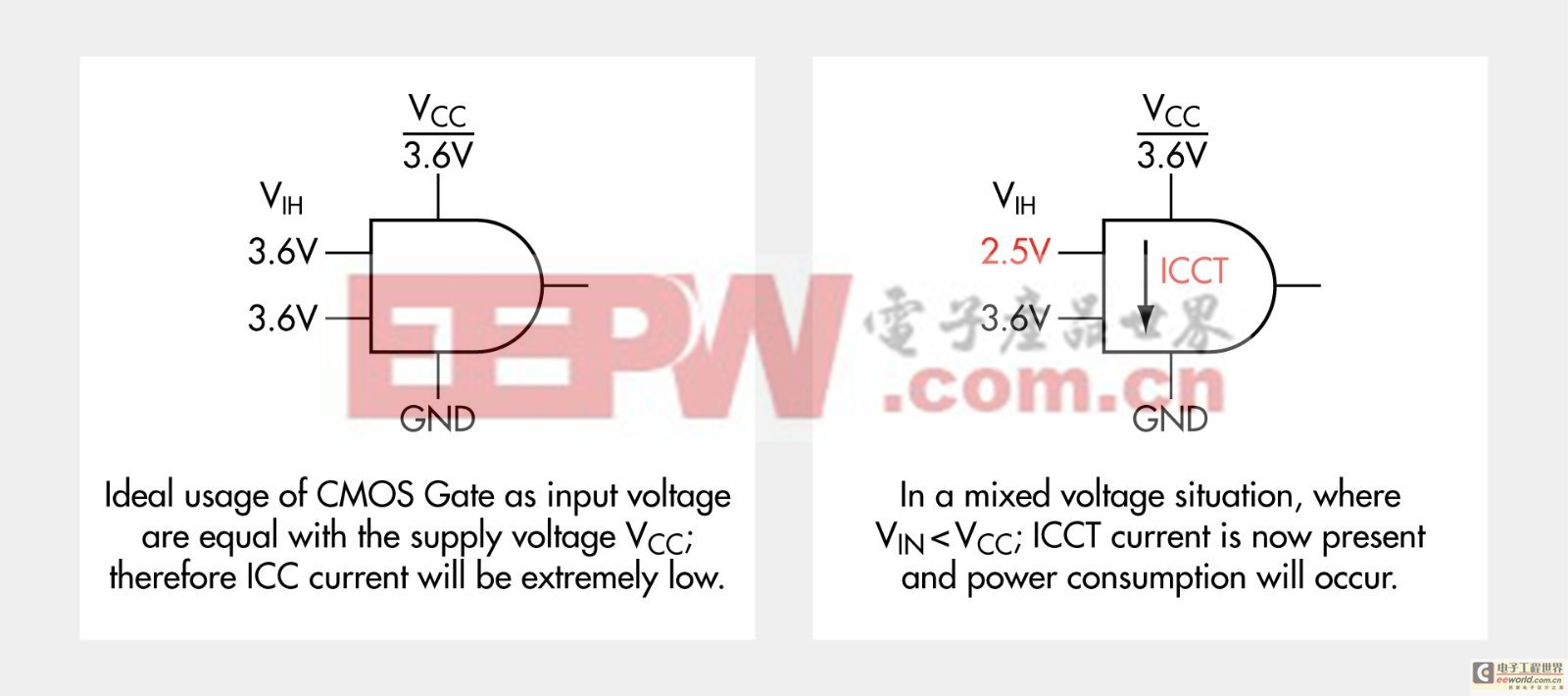

目前,大多数便携设备都备有多个电源轨,但在输入高电平(VIH)低于电源电压(VCC)时,仍可能产生不定功耗。当输入电压为电源轨电平(VIL = Gnd 或 VIH = VCC)时,CMOS一般具有极低的静态ICC和泄漏电流,故是移动应用中

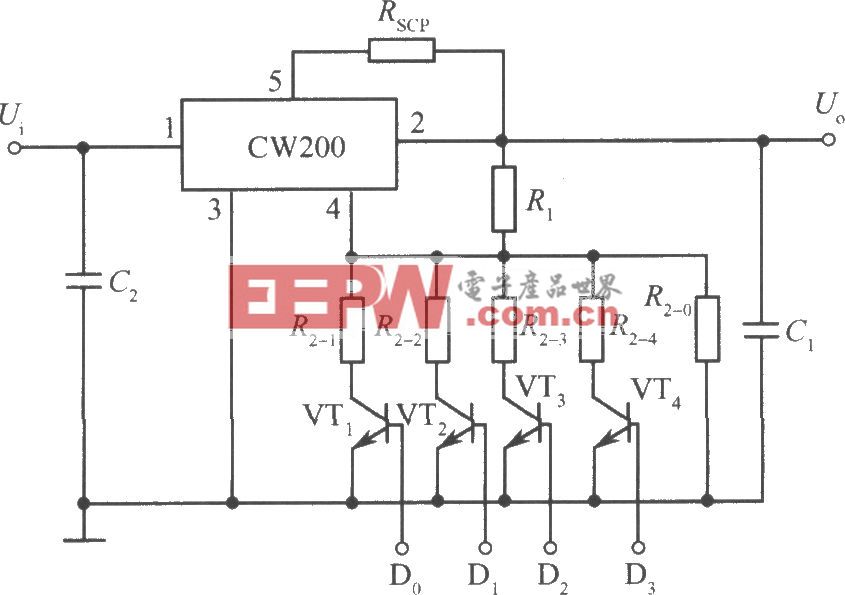

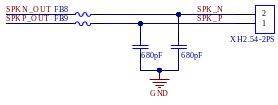

逻辑器件的首选技术。不过,若VIH VCC,会发生这种情况:输入级的PMOS和NMOS晶体管可能均在不同级“导通”,此时传导电流,在这个状态期间,静态电流ICC增加,存在一条从VCC到Gnd的路径。这个增加的电流被称为ICCT电流,亦是输入电压逼近阈值时的电源电流。图1描述了这种情况。

图1

逻辑门和输入电压条件

注释:*输入电压等于电源电压Vcc时为使用CMOS门电路的理想状态;这时ICC电流极低。

*在混合电压情况下,若Vin VCC,ICCT电流出现,功耗也随之产生。

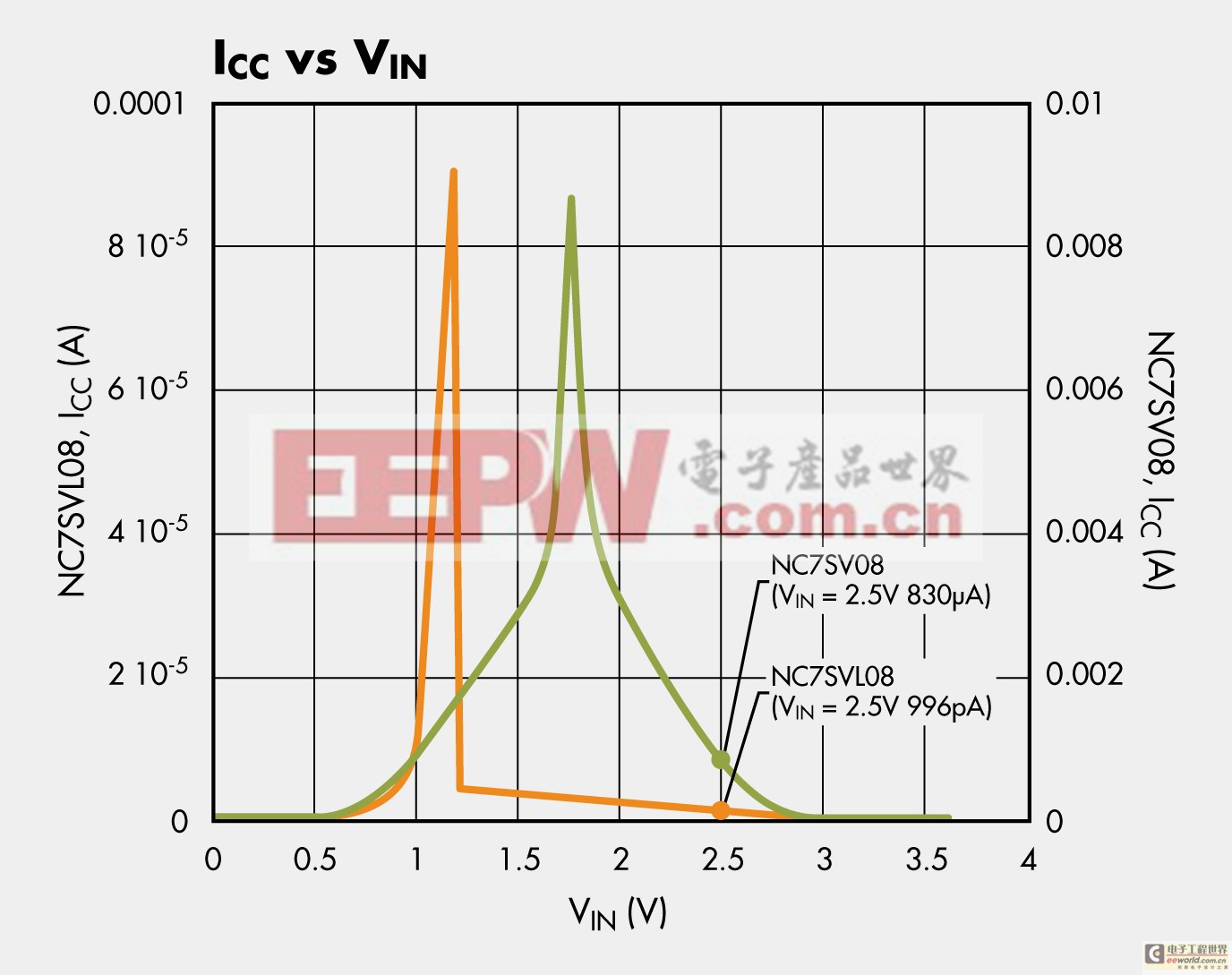

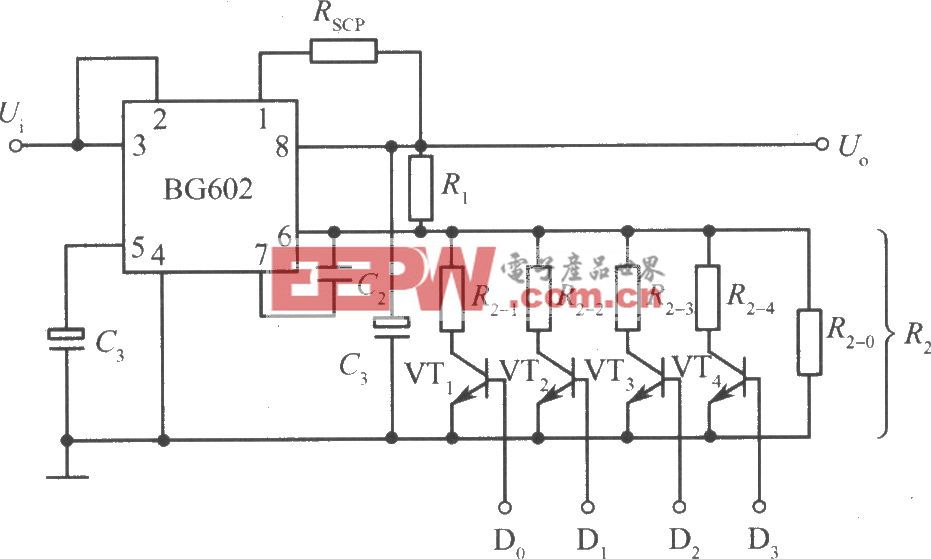

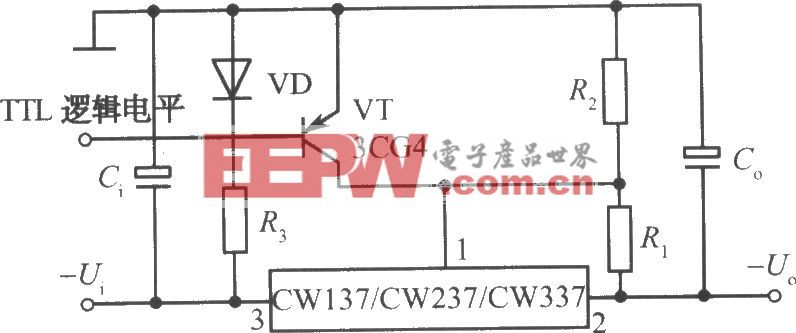

一般在CMOS门电路的设计中,输入电压阈值或输入切换点为VCC/2;不过,飞兆半导体的低ICCT门电路采用专有的输入电压设计,可降低输入阈值电压,增大输入电压范围,同时不影响有效逻辑低电平VIL。如前所述,当输入电压为0V或VCC时,CMOS门电路的耗电量极低,而产品数据手册通常会注明该条件下的ICC。因此,系统设计人员在VIH值小于VCC时看到ICC电流增大可能颇为惊讶。图2显示了一个重新设计的输入结构的优点。

VIN - ICC图比较了一个标准CMOS输入器件(红色线条)和一个低ICCT输入器件(蓝色线条)。静态功率由基本DC功率公式决定:P = ICC * VCC。在本例中,输入VIH为2.5V,标准CMOS门电路输入的功耗等于3.0mW (3.6V x 0.83mA) ,而低ICCT门电路的功耗只有0.003mW (3.6V x 0.99uA);也就是说,利用Low ICCT器件,静态功耗降低了100%。

图2 ICC -VIN输入曲线 (Vcc = 3.6V, VIN = 2.5V)

ICC电流的增大十分重要,因为它会大幅度增加器件的静态功耗。飞兆半导体的专有低ICCT输入结构可在ICCT电流出现期间限制其范围,如图2所示。

表1 不同VIH条件下的节能潜力

|

ICCT 电流

|

||||

|

VCC

|

VIN

|

标准 CMOS 门电路

|

低ICCT 门电路

|

节能

|

|

3.6

|

3.6

|

5.1 nA

|

1.5 nA

|

70%

|

|

3.6

|

2.5

|

830 uA

|

996 pA

|

100%

|

|

3.6

|

1.8

|

7.0 mA

|

2.7 uA

|

100%

|

|

3.6

|

1.5

|

2.8 mA

|

3.5 uA

|

100%

|

|

2.5

|

2.5

|

1.2 nA

|

983 pA

|

23%

|

|

2.5

|

1.8

|

21.4 uA

|

39.2nA

|

100%

|

|

2.5

|

1.5

|

417 uA

|

577 nA

|

100%

|

|

1.8

|

1.8

|

835 pA

|

656 pA

|

21%

|

|

1.8

|

1.5

|

2.6 nA

|

713 pA

|

73%

|

|

1.8

|

1.2

|

2.6 uA

|

4.6 nA

|

100%

|

表1比较了不同VCC/VIN条件下的ICCT电源电流级。从表中可看出,飞兆半导体的低ICCT门电路具有很大的节能潜力。在混合电压系统中,利用低ICCT门电路,与逻辑门电路相关的功耗可降至微不足道。

请参考表2列出的低ICCT门电路供货情况。根据需要可以提供额外的功能。当现有应用因前面讨论的输入条件而出现功耗过大时,用户可利用标准引脚输出,直接简便地进行替换。

表2 飞兆半导体的NC7SVL 低ICCT门电路

|

相关推荐技术专区 |

评论