基于FPGA+MATLAB的串行多阶FIR滤波器设计

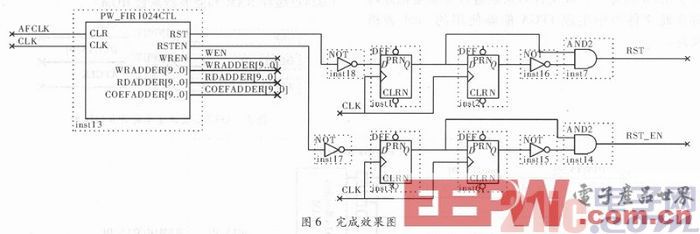

时序控制单元是设计的核心部分。AFCLK作为整个FIR滤波器系统的启动信号,此模块检测到AFCLK上升沿到来时会进行以下几个步骤的处理:(1)首先启动WEN写使能信号把当前DIN写入缓存中,写地址WRADDER累加一次。(2)然后启动读地址计数器RDADDER开始进行1 024次计数,同时把信号缓存和系数ROM中的数据送到乘加器中做1 024乘加运算,RST的作用是在第一个有效数据到来时进行累加器清零,RST_EN的作用是在完成1 024次运算时,准确地把结果锁存到输出端口,如图6所示。

本文引用地址://m.amcfsurvey.com/article/236081.htm

因为语音信号数据位宽是16位,经过1 024次乘加,和滤波器系数是32位整型量化处理的所有最终结果要做必要的量化处理,以得到正确的结果。

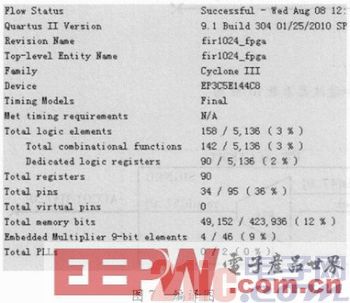

经过编译综合后,发现占用逻辑单元158,仅占EP3C5逻辑单元的3%,RAM单元约占12%,9位乘法器4个,如图7所示,效果理想。

4FPGA数字滤波器功能仿真验证

QuartusII不支持Testbench,采用*.vwf文件进行仿真需要手工输入激励,人工检查输出结果,此程序反馈,且效率较低。由于Quartus II的工程文件都是文本文件,所有的数据都以文件形式存储,所以可以编写文本过滤程序,将文本文件中的有用数据提取出来,然后进行后期处理,既提高了灵活性,又提高了效率。

QuartusII支持*.vwf、*.vec等激励输入,由于*.vec的文本操作性优于*.vwf文件,所以文中选择*.vec文件作为激励输入。使用Matlab产生8 000 Hz速率800 Hz,1000 Hz,1 300 Hz共3种频率的混合信号的仿真样本序列,带入到QuartusII中进行仿真,产生的仿真文件再导出到Matlab中进行显示,结果如图8所示。

由图中可以看出,经过FPGA滤波过后,800 Hz和1 300 Hz的信号都被滤波器滤除,仅有1 000 Hz信号保留。

5 结束语

通过设计实例,介绍了高速串行多阶FIR滤波器的设计思路和流程。仿真结果说明,FPGA在FIR数字滤波器实现方面相比通用和专用DSP芯片具有更灵活的使用方法,可以做到速度和逻辑资源占用方面的均衡。

滤波器相关文章:滤波器原理

fpga相关文章:fpga是什么

滤波器相关文章:滤波器原理

电源滤波器相关文章:电源滤波器原理

数字滤波器相关文章:数字滤波器原理

评论