车载GPS导航系统设计

当GPS採用差分定位(DGPS)的辅助定位模式,如美国的WAAS或欧洲的EGNOS系统时,则需输出RTCM或NTRIP 1.0的协定格式。此外,由于不同的接收机所提供的原始资料格式通常会不同,当有需要针对不同型号接收机收集的资料进行统一处理,就必须建立 GPS 通用资料交换格式,目前业界普遍採用的格式为RINEX。

GPS硬体架构选择要领

综上所述,一部车载GPS的硬体系统架构中,主要的单元包括天线、RF前端、基频/相关器、处理器核心,此外,还包括记忆体、匯流排介面。这些单元可以採离散式(discrete)的作法来提高设计上的弹性,也能採整合式的策略,将多个单元整合为一颗系统单晶片(SoC)、单封装(SiP)或模组,以降低设计的难度及成本。

当系统工程师在进行设计时,必须在效能、成本与弹性三大评量要件中进行选择。以效能来说,GPS接收器的效能指标有四项,分别是:准确性(Position accuracy)、灵敏度(Sensitivity)、第一次定位时间(Time to first fix,TTFF)及通道数量(channel number)。当这四项效能指标都要求达到最高时,就必须强调接收器的处理器效能、相关器通道数量、记忆体容量及高速的对外连结介面,如此一来,产品的成本自然会大幅提升,这时大众市场未必能够接受,因此往往必须做一些必要的妥协。

目前的技术已能将GPS接收器架构中的射频及基频整合在一起,而高整合度的产品能提供更佳的成本效益。以ST的STA2056为例,它将基频与射频功能整合于小型的QFN-68封装之中。它在基频部分採用ARM7TDMI为核心,时脉可高达66MHz;在射频部分为主动天线系统,含有易与被动天线连接的介面;此外,它还内建ROM及SRAM记忆体。由于只需要用到少数的外部元件,因此能降低总体物料(BOM)成本;其小尺寸能让产品设计更为轻薄短小,而且具有低功耗的优势;不仅如此,此类整合性产品也让工程师省下调校射频与基频整合的研究心力,能加速产品上市时间。其架构请参考(图二)。

图二. 具成本效益的GPS接收器架构,以STA2056为例

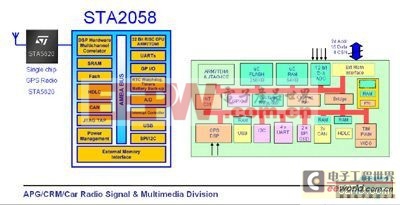

如果强调设计上的弹性,通常会选择射频与基频分离的方案,在基频元件方面还会嵌入Flash的记忆体,并支援较丰富的匯流排介面。以ST的STA2058为例,它整合了32位元微处理器ARM7TDMI和一个嵌入式快闪记忆体(embedded flash),并广泛支援CAN、SPI、UART、I2C、USB等介面,以及RTCA-SC159/WAAS/EGNOS等GPS系统。此外,STA2058EX更拥有外接记忆体介面,可以用作远端资讯处理服务平台,允许免黏接逻辑(glueless)而与外部装置(如:GSM/GPRS模组、晶片卡、音频功能DSP)相连,非常适用于车辆应用。其架构请参考(图三)。

图三. 具弹性的GPS接收器架构,以STA2058为例

评论