用于车速传感器性能测试平台的以太网桥设计

通过新旧测试平台对比,可以看到测试设备和后台管理计算机两大部件在性能和成本上基本相同。所以新测试平台的性能好坏和成本高低很大程度上取决于新引入的嵌入式串行口-以太网桥的性能和成本。目前嵌入式产品市场上此类网络设备大多是基于高档微处理器和实时操作系统开发的,其价格昂贵,且提供的串行口也只有1~2个,不适合需将多个串行口设备集中接入以太网,同时又要控制成本的应用场合。本文根据这类具体的应用需求在8位微控制器平台上设计了一种提供多个串行口的低成本嵌入式串行口-以太网桥。下面对其硬件和软件系统设计进行介绍。

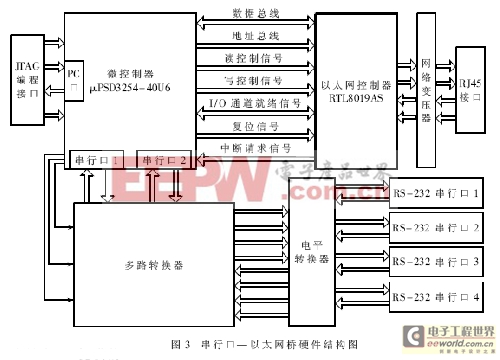

3.1 硬件系统设计

实现本系统所用串行口-以太网桥的功能,需要进行多个串行口设备的以太网接入,以及串行通信协议和以太网通信协议的相互转换。所以硬件电路设计主要包括多路串行口电路模块和以太网接口电路模块设计。本文硬件系统方案选用ST公司的工业级SoC型微控制器uPSD3254和Realtek公司的高性能以太网控制器RTL8019AS两大核心器件进行电路设计。硬件系统设计如图3所示。

其中是一款由8051内核模块和PSD模块构成的具有SoC特征的增强型高速微控制器。晶振频率最高可达40MHz,芯片内的PSD模块为用户提供了丰富的可配置存储器资源(256KB主Flash、32KB次Flash及32KB的SRAM)、灵活的DPLD地址译码电路以及3000门的CPLD模块电路,片内硬件看门狗大大提高了系统可靠性,芯片自带JTAG接口支持ISP在系统编程,方便了程序调试和下载;而RTL8019AS是一款非常成熟的基于ISA总线、NE2000兼容的高性价比10M以太网控制器,其本身能完成以太网协议处理,只需和微控制器进行简单连接即可实现以太网通信;另外硬件电路还包括MAX232电平转换器和20F001N网络滤波器等少数外围器件。整个硬件系统仅由4、5个芯片构成,结构简单紧凑,可靠性高,成本低廉。下面从三方面给出硬件电路的具体设计。

3.1.1 PSD模块配置设计

微控制器uPSD3254的PSD模块使得硬件电路的设计大为简化。它本身提供的两块大容量Flash以及SRAM(支持后备电池)使用户无需再进行外部程序/数据存储器扩展。同时PSD模块中的DPLD子模块为Flash和SRAM提供了灵活的地址译码, CPLD子模块可供用户设计一些简单的组合/时序逻辑电路。本设计根据具体应用需求,对PSD模块配置如下:

(1)主Flash扇区0(fs0)配置在程序存储器的0000H~FFFFH空间;

(2)主Flash扇区1(fs1)配置在程序存储器的8000H~7FFFH空间;

(3)SRAM(rs0)配置在外部数据存储器的0000H~7FFFH空间;

(4)CPLD的PA口和PB口被分别设计为两个多路转换器,以供串行通信时进行信道切换。

3.1.2 串行口扩展设计

由图2可知,车速传感器性能测试平台中四个仅支持串行口的测试设备(分别负责耐温、转速、传感器静态特性和动态特性的测试)要同时接入嵌入式串行口-以太网桥,而微控制器?滋PSD3254本身只提供两个串行口(uart0、uart1),所以必须进行串行口扩展。一种简单的扩展方法是利用单片机I/O端口控制多路转换器(如CD4052)进行串行口扩展(图3),实现了一点对多点分时串行口通信。根据微控制器的I/O端口资源情况,依此方法系统最多可扩展32个串行口。根据此思路并结合测试平台的具体应用需求,利用uPSD3254的CPLD模块设计了两个二选一的多路转换器,从而不仅将两个串行口扩展为四个(uart00、uart01和uart10、uart11),而且省去了多路转换器芯片。另外,电平转换器实现TTL—RS232电平转换,这样就为四个测试设备提供了四个标准RS-232串行口供其接入串行口-以太网桥。

3.1.3 以太网接口设计

以太网接口是硬件电路设计的关键。因为RTL8019AS是基于ISA总线PC主板的以太网控制器,所以在和8位微控制器进行接口(见图3)时其硬件电路与通用方式有很大不同。下面从RTL8019AS以太网控制器[1]自身功能配置、与微控制器之间的总线接口及与网络介质的接口等三方面给出具体电路设计。

(1)RTL8019AS功能管脚设置

RTL8019AS提供3种工作方式:PnP即插即用方式、免跳线方式和跳线方式。由于8位微控制器无法支持PnP工作方式,而免跳线方式又需外加专用串行E2PROM 93C46以存放相应的工作参数,因此选择跳线工作方式。在这种方式下RTL8019AS的中断、I/O端口地址、网络接口类型选择等就完全取决于表1所示功能管脚的状态。

JP脚接高电平使芯片工作于跳线方式,IOCS16B脚接低电平选8位数据总线,IRQS0~IRQS2接低电平选INT0为中断请求源,IOS0~IOS3接低电平选芯片I/O端口基地址为300H,AUI、PL0、PL1接低电平分别选BNC网络接口和10Base-T双绞线传输介质,SMEMRB/SMEMWB接高电平屏蔽BROM读写操作。

评论