论NIOS-II系统中A/D数据采集接口的设计与实现

由ADC0804的时序可知,转换过程由一个写信号启动,转换完成后,输出INTR信号,此时可以读取数据。之后即可进入下一个转换周期。由ADC0804的转换时间可知,其最大采集频率为10KHz,只要用户设置的采样频率不超过这个数值,ADC0804就可以正常的工作。因此设计时要注意两点:①写信号的频率要低于ADC0804的最大转换频率;②在写信号之后至少要有100ms的时延,才能输出读信号。

在此,提出两种方法来实现ADC0804的控制信号时序:①主动模式—控制电路启动A/D转换后,在INTR信号的作用下,输出读信号,同时从ADC0804的数据总线上读入数据,之后输出一个写信号,开始下一次转换。②被动模式—ADC0804的读写信号完全由控制电路按照固定的时序产生,与其自身输出无关。

数据接口

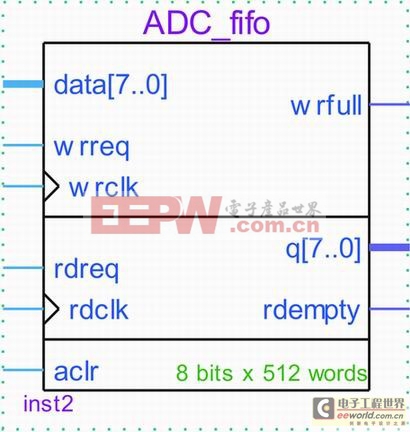

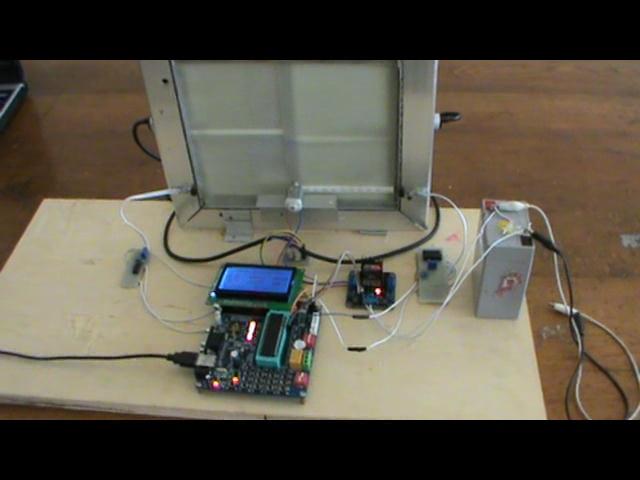

相对于AVALON总线信号来说,A/D采样的速率非常低,而且,AVALON总线的接口信号和ADC0804数据输出的接口信号时序不一致。因此,要实现满足要求的数据通道,要做到两点:①数据缓冲,实现速率匹配;②信号隔离,实现接口时序的转换。解决这两点,可以将两端口通过一个异步的FIFO连接,该FIFO应该是可以在不同的时钟信号下进行异步的读写。这样的一个FIFO的实现可以在Quartus-II里面用ALTERA公司提供的FIFO Core进行定制。在本设计中,定制的FIFO模块如图3。

图3 FIFO模块

评论