ARM指令寻址方式之: 内存访问指令寻址

6.[Rn],±Rm>

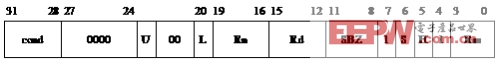

(1)编码格式

指令的编码格式如图4.29所示。

图4.29 杂项内存访问指令——后索引寄存器偏移寻址编码格式

指令访问地址为实际的基址寄存器的值。当指令的执行条件满足时,将基址寄存器的值加/减索引寄存器Rm的值回写到Rn基址寄存器。

(2)语法格式

LDR|STR{cond>}H|SH|SB|D Rd>,[Rn],±Rm>

其中:

· Rn为基址寄存器,该寄存器包含内存访问的基地址;

· Rm>为偏移地址寄存器,包含内存访问地址偏移量。

(3)操作伪代码

Address = Rn

If conditionPassed{cond} then

If U = = 1 then

Rn = Rn + Rm

Else

Rn = Rn – Rm

(4)说明

① 程序寄存器r15被指定为Rm或Rn,指令的执行结果不可预知。

② 如果Rm和Rn指定为同一寄存器,指令的执行结果不可预知。

4.2.3 批量Load/Store指令寻址方式

批量Load/Store指令将一片连续内存单元的数据加载到通用寄存器组中或将一组通用寄存器的数据存储到内存单元中。

批量Load/Store指令的寻址模式产生一个内存单元的地址范围,指令寄存器和内存单元的对应关系满足这样的规则,即编号低的寄存器对应于内存中低地址单元,编号高的寄存器对应于内存中的高地址单元。

指令的语法格式如下。

LDM|STM{cond>}addressing_mode> Rn>{!},registers>^>

指令的寻址方式如表4.6所示。

表4.6 批量Load/Store指令的寻址方式

格 式 |

模 式 |

|

1 |

IA(Increment After) |

后递增方式 |

2 |

IB(Increment Before) |

先递增方式 |

3 |

DA(Decrement After) |

后递减方式 |

4 |

DB(Decrement Before) |

先递减方式 |

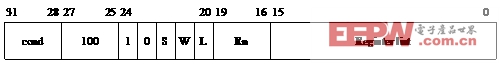

指令的编码格式如图4.30所示。

图4.30 批量Load/Store指令编码格式

编码格式中各标志位的含义如表4.7所示。

表4.7 批量Load/Store指令编码格式各标志位含义

位标识 |

取 值 |

含 义 |

P |

P=0 |

Rn包含的地址,是所要访问的内存块的高地址(U=0)还是低地址(U=1) |

P=1 |

标识Rn所指向的内存单元是否被访问 |

|

U |

U=0 |

Rn所指内存单元为所要访问的内存单元块的高地址 |

U=1 |

Rn所指内存单元为所要访问的内存单元块的低地址 |

|

S |

S=0 |

当程序计数器PC作为要加载的寄存器之一时,S标识是否将spsr内容拷贝到cpsr;对于不加载PC的load指令和所有store指令,S标识特权模式下,使用用户模式寄存器组代替当前模式下寄存器组 |

S=1 |

||

W |

W=0 |

数据传送完毕,更新地址寄存器内容 |

W=1 |

||

L |

L=0 |

Store指令 |

L=1 |

Load指令 |

评论