一种毫米波CMOS射频芯片嵌入式偶极子天线

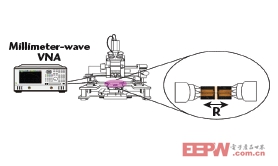

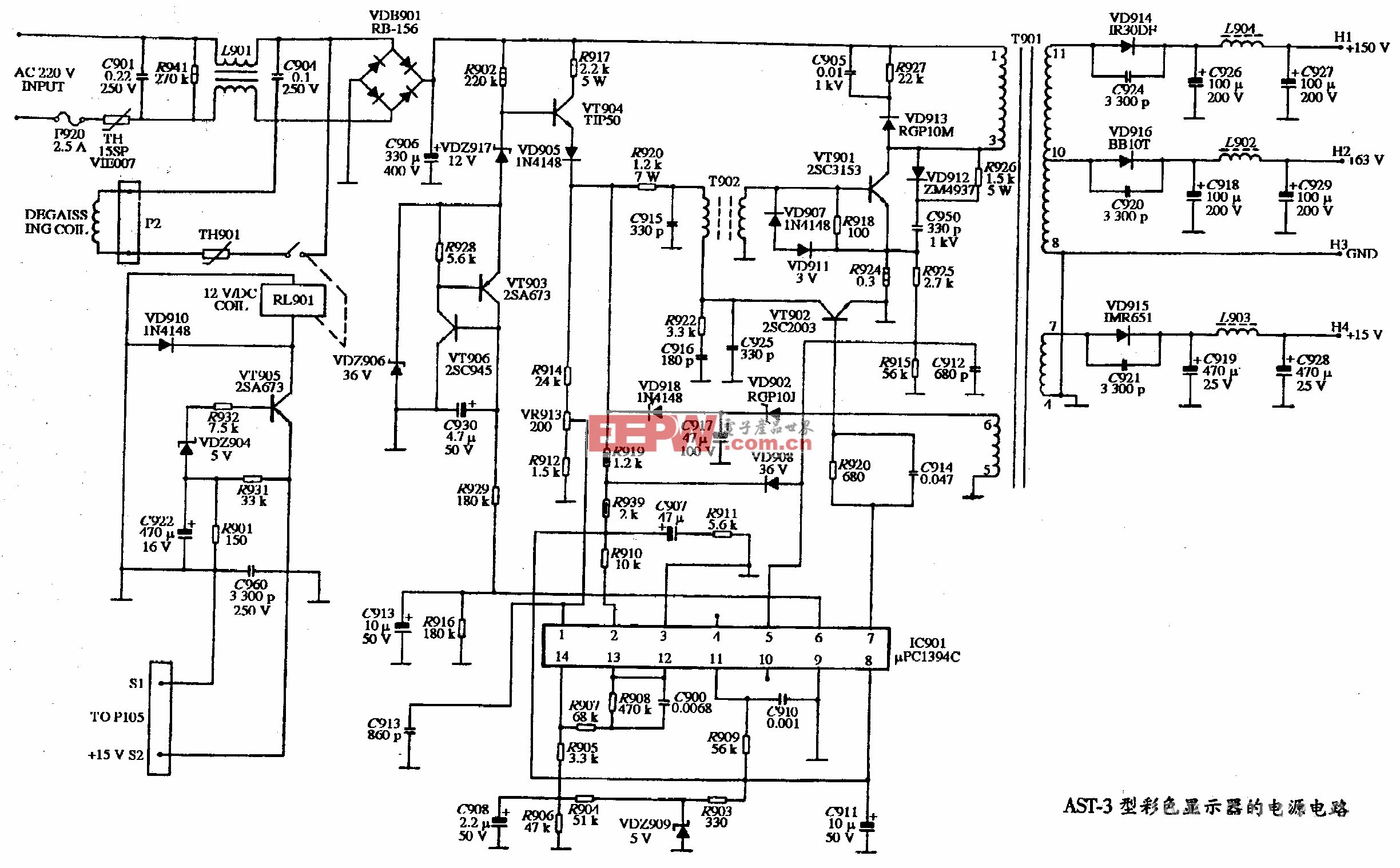

仿真天线辐射效率近似为百分之16。这可能是CMOS基底损耗造成的。H平面图样除了在某个特定方向存在一些衰减之外近似为全向图样。H平面仿真最大,最 小和平均增益分别近似为-9,-16和-11dBi。用Simons和Lee描述的技术测得晶圆上测量天线绝对功率增益。如图7所示,两个相同的射频芯片 嵌入式天线面对面距离R放置。其中一个天线为发射天线,而另一个为接收天线。分隔两相同天线的距离R应满足远场条件,即大于等于

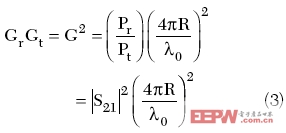

这里D和λ0分别为射频芯片嵌入式天线最大孔径与工作频率自由空间波长。从Friis的功率传输公式得知,最大功率天线增益(在偶极子天线的中心前向上)由下式给出:

这里

Gt和Gr =发送和接收天线增益

Pt =发送功率

Pr =接收功率

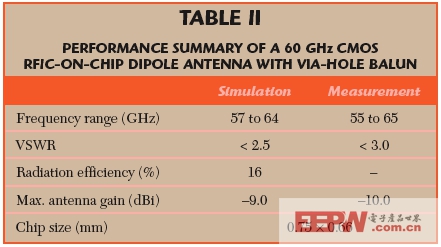

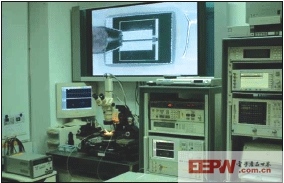

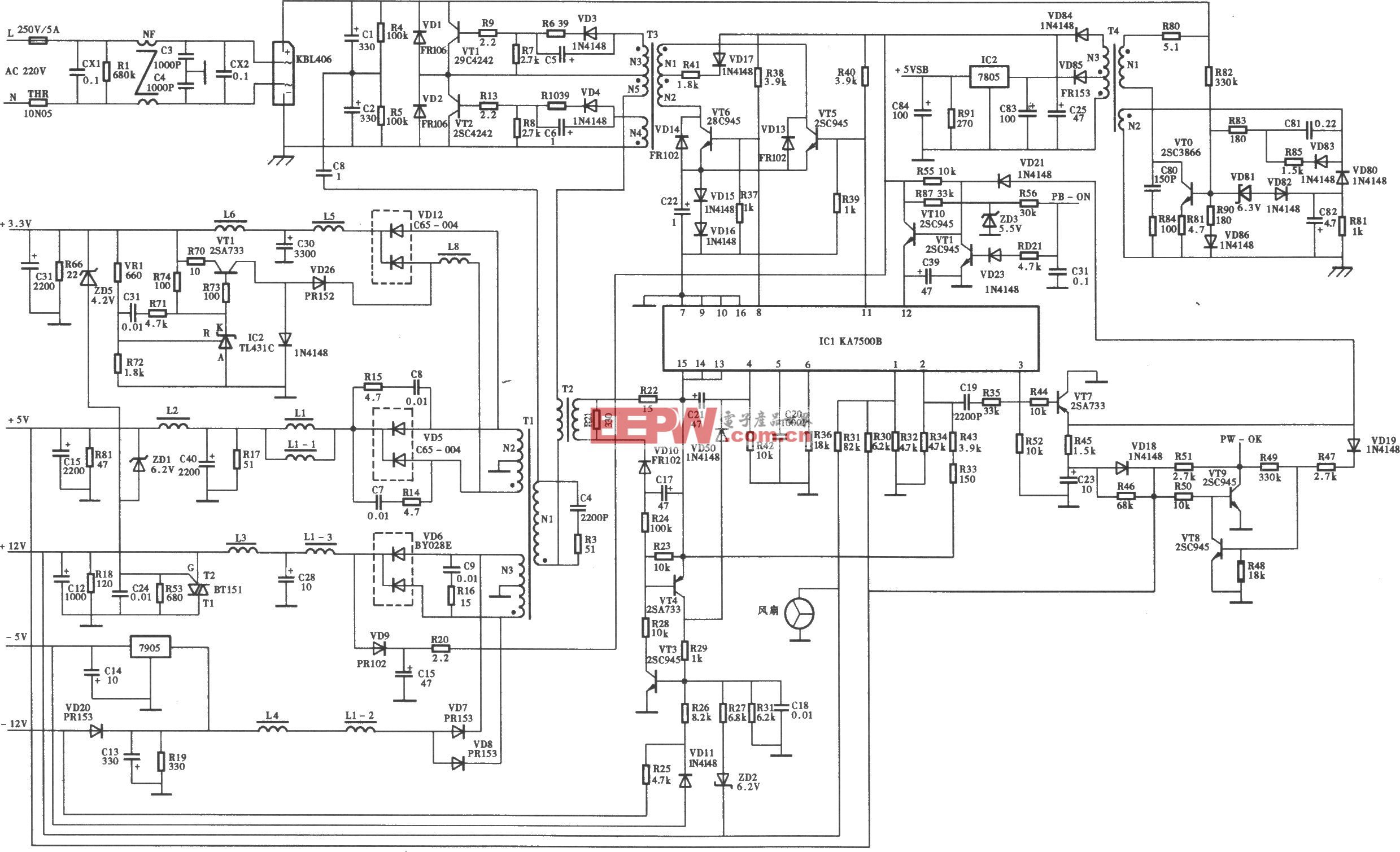

同样,因为两天线相同,Gr= Gt=G。功率比Pr/Pt为由VNA得来的实测直接传输系数|S21|2。图8给出了晶片上测量设置的探针台显微图。60GHz实测最大天线功率增益约为-10dBi。这与仿真结论完美一致。表2给出了天线辐射特征的性能总结。

|

| 图7 射频芯片嵌入式天线晶片上测试的配置图示 |

结论

本文讨论了一种带有集成微带过孔不平衡-平衡器,60GHz毫米波CMOS射频芯片嵌入式偶极子天线的设计,制造和晶圆上测量。这是为了利用集成低成本单 片集成CMOS射频前端电路的天线为60GHz无线电实现一种射频芯片嵌入式系统(SoC)。天线芯片使用0.18微米CMOS工艺制造,芯片尺寸为 0.75 × 0.66 mm。

使用了基于FEM的一种3D全波EM solver—HFSS进行设计仿真。对输入VSWR和射频芯片嵌入式天线的最大天线功率增益做了晶圆上测量。实测天线VSWR在55到65GHz之间小 于3。实测H平面辐射图样近似为全向图样,而且仿真天线辐射效率近似为16。这可能是CMOS基底损耗引起的。60GHz处实测天线功率增益约为 -10dBi,这与仿真结果很好地一致。今后将会获得所设计的带有60GHz CMOS射频前端电路的60GHz射频芯片嵌入式天线的集成产品。

|

|

| 图8 探针台晶圆测试设置 |

申明

作者想感谢台湾National Science委员会芯片制造中心(CIC)在TSMC CMOS工艺方面的帮助。

评论