一种基于FPGA的振动信号采集处理系统

4.2 数据流开关

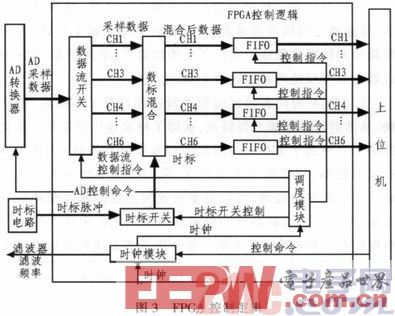

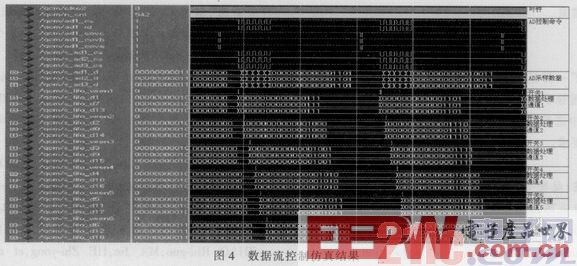

本文引用地址://m.amcfsurvey.com/article/262772.htm采样数据处理的实时性是FPGA设计中首先要考虑的问题,振动信号采集过程中常会由于输入数据量过大,导致后续处理电路处于饱和状态以致数据丢失。为解决上述问题,FPGA通过开关切换的方式将数据分别送入不同的线程进行处理。振动传感器输出数据格式如下:(A1B1C 1D1E1F1),(A2B2C2D2E2F2),……(AN BN CN DN EN FN),A、B、C、D、E、F分别代表不同方向的振动量值。采用单通道的数据处理方式时,程序首先需完成数据的区分工作,然后完成6次数据处理过程,当一次需要处理数据量较大的情况下,系统会产生较大的延迟并导致后续数据的丢失。为降低数据处理电路的负担,采用数据流开关将振动传感器输出数据分别存储在不同的通道中通过数据流控制开关后数据格式如下:

通道1:A1、A2……AN;

通道2:B1、B2……BN;

通道3:C1、C2……CN;

通道4:D1、D2……DN;

通道5:E1、E2……EN;

通道6:F1、F2……FN。

仅需处理N个数据就能满足系统要求,系统对于处理能力的要求相应降低。数据流控制仿真结果如图3所示。图中AD采样数据为连续的单通道输入数据,经过AD控制命令和通道开关的控制后被分别发送到6个数据处理通道进行后续处理。

4.3 FIFO的控制

振动数据存储在由XILINX提供的FIFO软核中。FIFO核的存储深度、数据宽度、标志位设置、存储类型和读写端口速率可以在FIFO生成时进行设置,FIFO模块生成时占用FPGA内部的BLOCK RAM,即使存储容量很小的FIFO也会占用整块BLOCK RAM。FIFO端口包括输入输出端口、读写使能、读写时钟及空满标志几部分。其中,输入输出端口与数据总线连接用于数据传输;读写使能由控制逻辑驱动完成一次读写操作;读写时钟信号完成读域或者写域所有信号的同步;满标志表明由于该FIFO处于满状态,写操作将被忽略,空标志表明FIFO处于空状态,读操作将不能获得正确的数据。

FIFO控制逻辑进行数据写入操作时首先判断FIFO是否处于满状态,如果FIFO处于满状态,先从FIFO中读出一条数据,然后将新数据写入FIFO中。如果FIFO不处于满状态则直接进行写操作。FIFO读操作的时机由DSP控制,DSP内的程序首先读取空状态寄存器判断FIFO中是否存有数据,如果寄存器显示FIFO为空则取消读操作,否则就从FIFO中读出需要的数据。IP核对使能信号的访问时序有着严格地要求,使能信号必须于读写时钟完全同步,而且控制逻辑将使能信号的长度控制在一个读写时钟周期内。

4.4 数据的存储

振动采样数据的数据量非常庞大,一旦出现错位将无法完整复现信号的原始状态,因此在对数据进行存储的同时,对数据进行时间标记也是十分重要的。时间标记在一个完整的记录周期结束时进行,调度模块控制时标开关在所有的FIFO中存入时标信息,FIFO中存储在时标以前的数据均为本周期的数据,存储在时标信息以后的数据均为下一周期的数据,时标及数据记录格式如表1所示。表中D15,D14位是保留位用于功能扩展,D13,D12是表明存储数据是时标信号(01、02),或者采样数据(00)。

4.5 数据的访问

DSP进行数据还原时,访问程序依据采集顺序先从本周期起始通道开始依次读出采样数据,当访问程序读取到第一个时标数据后本周期数据读取完毕,访问程序继续读取后续通道的时标信息,直至获得所有通道的时标数据后表明本次数据访问过程结束,如果访问程序连续获得了所有通道的时标信息表明采样数据为完整有效的数据,否则说明在采样过程中存在数据丢失的现象,数据不可信不能进行后续处理,如果出现数据丢失现象则访问程序将所有通道时标数据读出后本次访问结束。

5 结束语

文中设计了一种基于FPGA的振动信号采集处理系统,通过数据流管理等手段实现振动信号的实时采集处理,本设计在真实环境中进行了验证,系统运行稳定可靠,各项性能指标满足技术要求。

模拟信号相关文章:什么是模拟信号

fpga相关文章:fpga是什么

低通滤波器相关文章:低通滤波器原理

电荷放大器相关文章:电荷放大器原理

离子色谱仪相关文章:离子色谱仪原理

评论