基于FPGA的LCD显示远程更新的设计方案及原理图

2.2结构和系统模型

本文引用地址://m.amcfsurvey.com/article/266849.htm(1)基本结构图

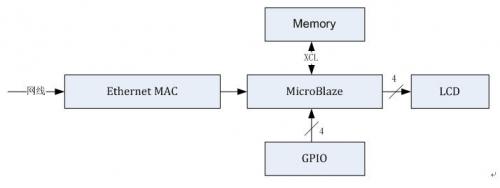

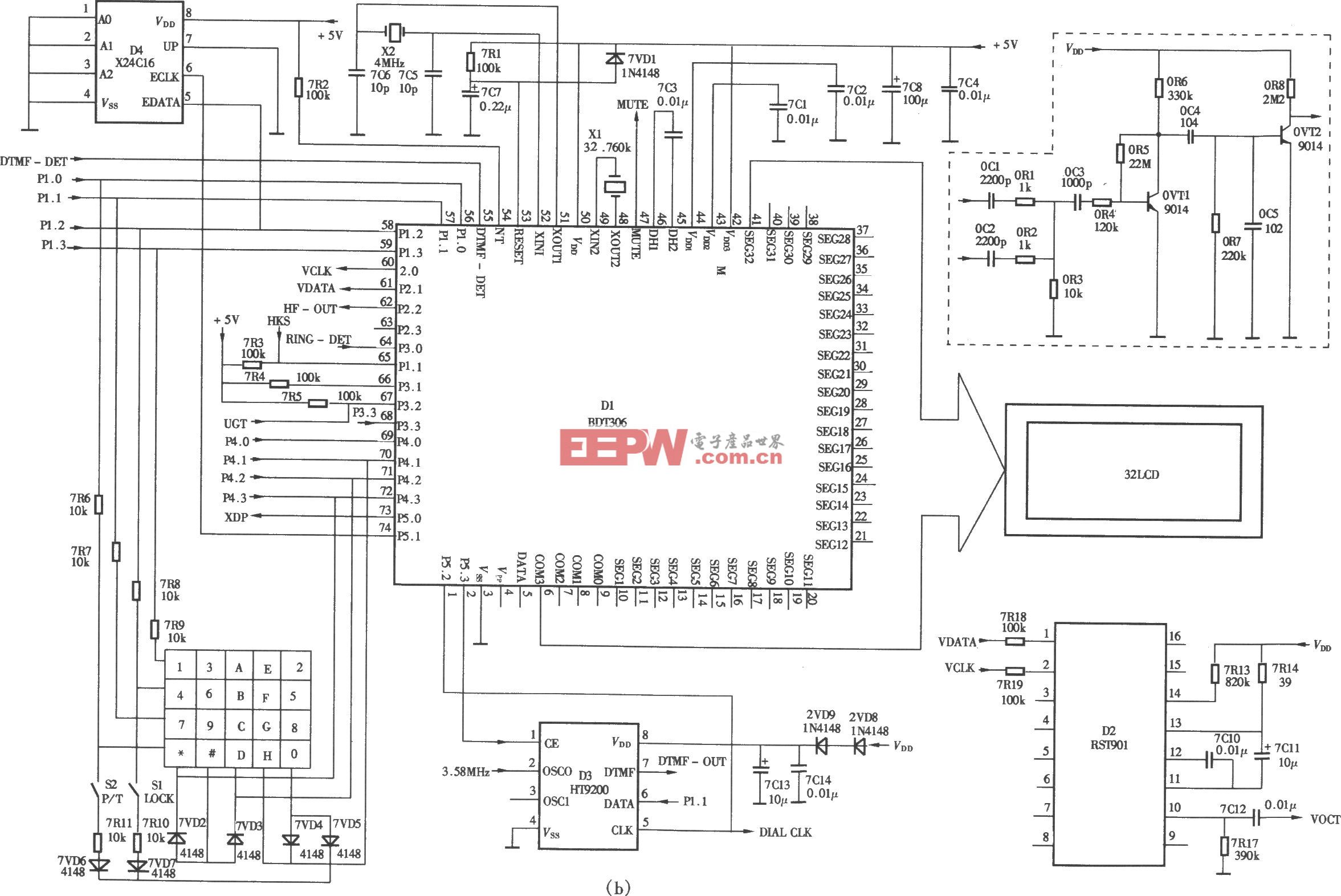

要显示的内容通过TCP/IP进行传输与更新,没有了距离的限制,可以在远程实现更新。需要更新的LCD显示内容共有四部分组成,在一段时间内LCD只能显示其中的一个部分,并循环进行显示。由Nexys3开发板上的四个按键控制跳转。Nexys3FPGA开发板通过RJ45口接收到信号后,PHY模块对IP包进行拆分,恢复成原始信号。由 MicroBlaze 软核存入Cellular RAM中,并按照顺序在LCD上进行分段显示。当MicroBlaze 检测到有按键按下时,MicroBlaze软核处理器响应中断,并进行中断处理,显示相应按键对应的部分信息,一段时间后,返回中断前的状态。

图2 基本图

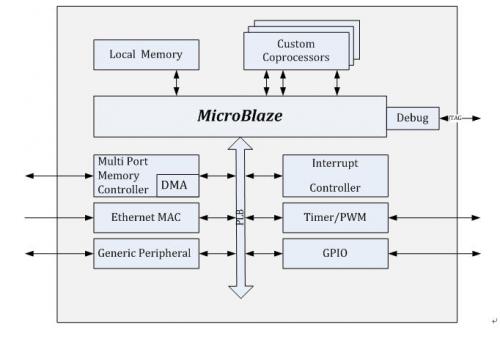

(2)MicroBlaze结构图

图3 MicroBlaze软核结构图

Ethernet MAC 接收计算机发送的数据后拆分IP包,然后送入MicroBlaze处理,由MultriProt Memory Controller控制存入 Local Memory中,然后按照顺序进行循环显示,显示时间由 Timer/PWM控制,当有按键按下时,通过GPIO传送入MicroBlaze软核,由 Interrupt Controller 控制进行中断,将当前信息存入堆栈,后跳转到按键指定处进行显示Timer/PWM控制显示一段时间后,返回中断前的状态继续正常循环显示.Customer Coprosser协助 MicroBlaze处理数据.

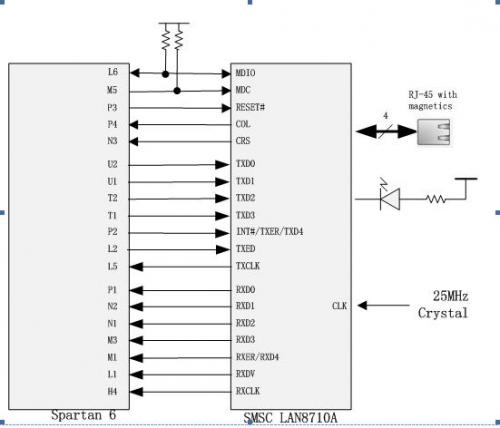

(4)以太网模块图

图4 以太网结构图

Nexys3基本系统生成器(BSB)支持包自动生成一个测试应用程序的以太网MAC。ISE的设计可以使用IP内核发生器用向导来创建一个以太网MAC控制器IP核。如果COL此信号置位时表示碰撞条件的检测MLL模式。在MLL模式中:

1.传输数据时的控制信号为TXCLK,当TXCLK为上升沿时控制器同步传输数据,TXEN为高电平时表明此时控制器传输的数据是有效的,若TXER为高电平时,说明传输检测到错误。

2.接受数据时,在RXCLK为上升沿时RXD[3:0]开始接受数据。控制信号RXCLK为上升沿接收数据时,接受信号RXDV为高电平。如果RXER为高电平时说接受检测到错误。

LCD显示屏相关文章:lcd显示屏原理

lcd相关文章:lcd原理

评论