基于FPGA的软件无线电平台设计

1.4 CPU控制单元

本文引用地址://m.amcfsurvey.com/article/269660.htmVirtex-4FX系列FPGA集成了运行速度高达450 MHz的双32位嵌入式PowerPC,每个处理器可提供超过700 DhrySTone MIPS的性能,是普通FPGA中处理器性能的三倍。两个完全集成的UNH认证的10/100/1000 Ethernet MAC进一步提升了Virtex-4FX处理平台的性能,从而提高了FPGA资源的可用性。本系统以PowerPC作为该系统的指令处理和控制单元,可以避免纯硬件设计复杂,通用性差和不容 易协调控制的缺点。PowerPC是本系统SoPC架构的核心组成部分,担负算法实现和中央控制两部分任务。Virtex-4FX内部有大量乘法器可供调用,能够充分满足各种数字信号处理要求;

PowerPC与前文提到用Verilog-HDL 设计的DSP模块连接,使整个系统具有实时动态信号的处理能力。PowerPC作为控制器的状态流程如图3所示。

2 FSK设计实例及仿真结果

在现代通信中,调制器的载波信号几乎都是正弦信号,数字基带信号通过调制器改变正弦载波频率,产生移频键控(FSK)信号。FSK时域表达式为

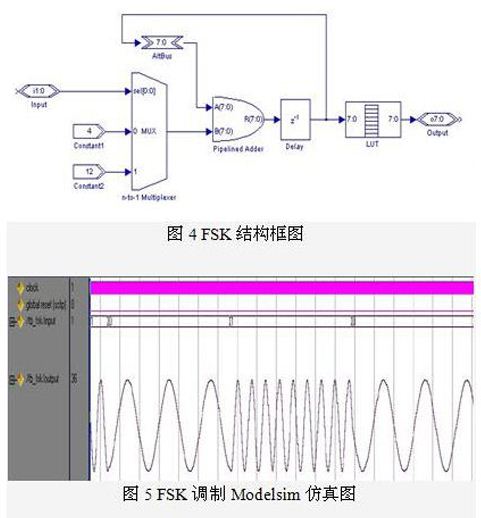

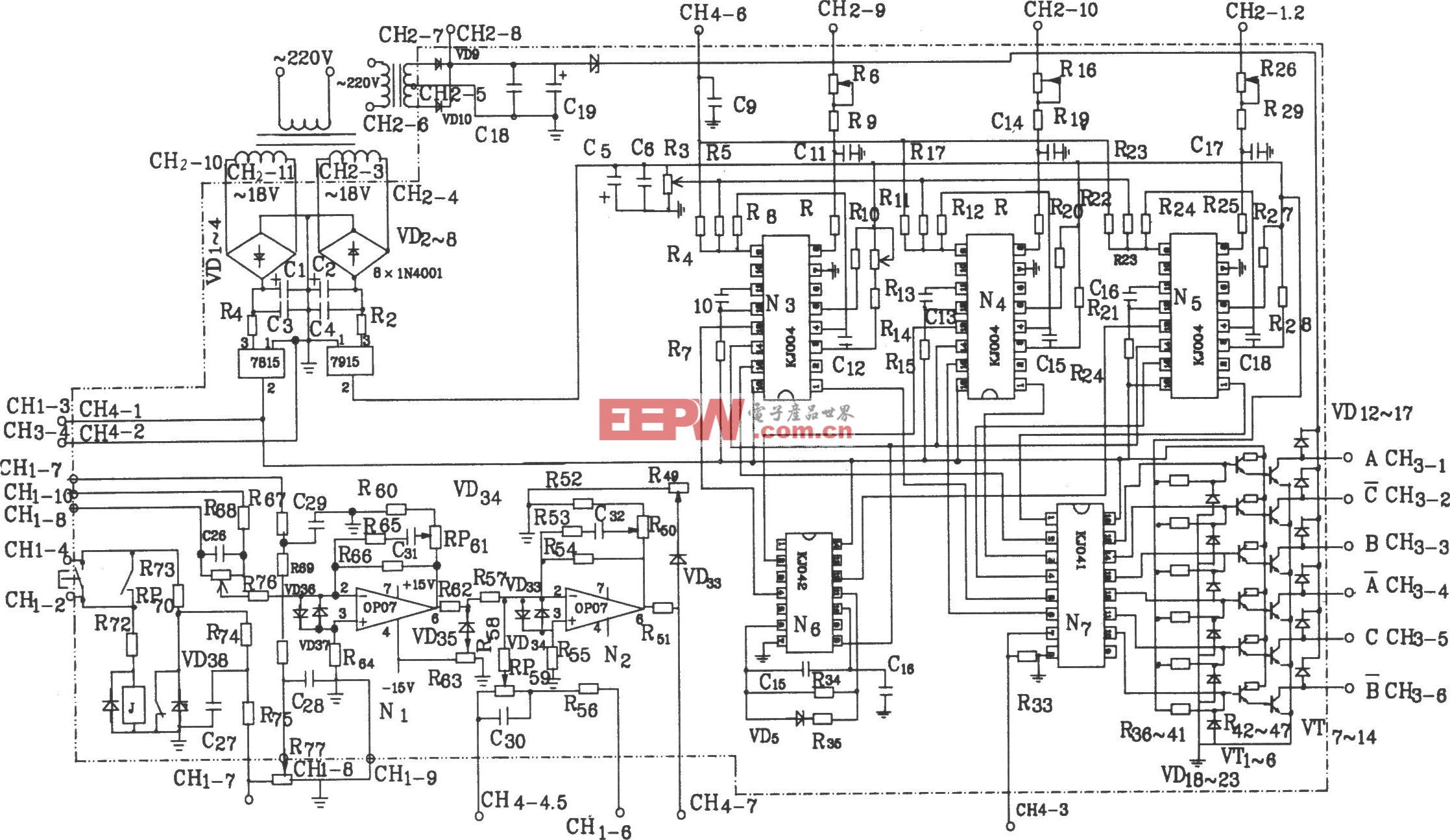

用本系统实现FSK调制结构框图如图4所示,用Verilog-HDL语言编写实现的FSK调制模块,相对于传统软件无线电的实现方式,省去了读取指令周期的时间,总运算时间缩短了一半。FSK调制的ModelSim波形仿真结果如图5所示。

3 结论

改进的基于FPGA的嵌入式软件无 线电系统,可更好地满足通信、雷达、数字电视等高科技领域对信号处理实时性的要求。运用软件无线电和SoPC技术,极大的提高了系统动态实时信号的处理能 力。在节约资源方面,以节省芯片数量计算,该系统相对于目前常规系统,节省功耗和体积可达30%以上。40MHZ时钟频率, 12bit精度,80dB无寄生动态范围,该系统可以应用于Cellular / PCS基站,多通道多模式接收机,GPS抗干扰接收机,相控阵接收机,频谱分析,3G无线通信等领域。

评论