基于FPGA的LZO实时无损压缩的硬件设计

3LZO压缩系统集成与测试验证

本文引用地址://m.amcfsurvey.com/article/273211.htm3.1LZO压缩系统硬件结构

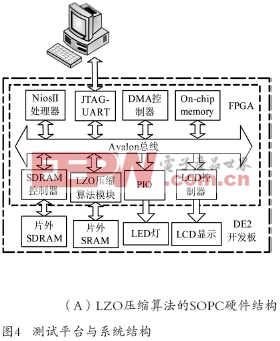

如图4(A)为LZO压缩系统SOPC硬件结构,内层虚线表示FPGA,虚线内的模块有相应的代码或硬件电路构成,外层虚线表示DE2开发板,开发板提供了相应的资源。图中:PC机通过下载线将待压缩的数据传送至DE2开发板上的SDRAM,数据经压缩后再经下载线回传至PC机;Nios II处理器负责与用户交互,对待压缩数据进行管理,控制整个SOPC的正常工作;JTAG-UART用于设计过程中的软件和硬件调试;DMA控制器用于高速数据传输,它将片外SDRAM中的待压缩数据传送到LZO压缩算法模块,将LZO压缩算法模块中被压缩后的数据传送到片外SDRAM中;LZO压缩算法模块用于对用户传输过来的数据进行压缩,它与片外SRAM进行通讯;LCD控制器用于控制LCD的显示,LCD可显示LZO压缩文件开始与结束,增加用户交互的可视性,例如显示待压缩文件的大小,压缩后的文件大小等;PIO控制LED指示灯的亮与灭,LED灯可用于指示LZO压缩文件开始与结束,增加用户交互的可视性;On-chip memory用于存储系统启动时的软硬件配置等信息;SDRAM控制器用于控制SDRAM与系统数据的交换;SDRAM用于存储指令和数据;SRAM用于存储LZO压缩算法过程中产生的压缩信息,在硬件设计中扮演字典的角色,采用片外SRAM的原因是考虑到FPGA片内资源可能不够使用;以上所有涉及到的模块均采用Avalon总线规范进行数据通信,它们共同挂载到数据总线上,Avalon总线具有自身的仲裁结构、地址分析等功能,易于用户集成开发。

3.2 开发板简介

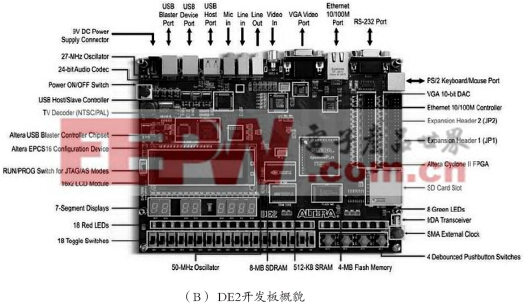

测试与验证平台如图4(B)所示的DE2开发板,该开发板上的核心芯片为Altera公司的Cyclone II EP2C35FPGA。选择该开发板作为测试平台主要基于以下考虑:拥有足够的片外存储资源(SDRAM 8MB、SRAM 512KB);拥有较丰富的片上逻辑资源(35K LEs);拥有丰富的可用于调试的外设(LCD、7-segment-displays);支持 Nios II嵌入式软核;成本较低。

3.3 测试结果及对比

针对LZO压缩算法模块和集成后的系统进行板级测试,一方面验证算法模块及集成后的系统的功能正确性,另一方面测试分析算法模块及集成后系统的性能。测试内容包括:数据压缩率(压缩后的文件大小/压缩前的文件大小),数据压缩速率(单个周期内处理的字节数)。

通过图5(A)可知,压缩率提升最大的是1.pdf文件,提升最小的是7.mp3文件(音频文件已经采用音频压缩算法压缩过了),除去最大值和最小值后取平均值,则压缩率提升为1.37%;通过图5(B)不难发现,压缩速率提升最快的为2.txt文件,提升最慢的为10.dll文件,除去最大值和最小值后取平均值,则压缩速率提升为4.81倍。

fpga相关文章:fpga是什么

网线测试仪相关文章:网线测试仪原理

评论