基于C8051F020的配电变压器监测终端设计

摘 要:文章主要介绍了以C8051F020单片机为核心的配电变压器监测终端的设计方案,并给出了硬件和软件的实现方法。

关键词:C8051F020;配电变压器监测终端

引言

配电变压器是将电能直接分配给低压用户的电力设备,其运行数据是整个配电网基础数据的重要组成部分。本文设计了一种集多功能电表、无功投切控制器、采集器等功能于一体的新型配电变压器监测终端。

硬件设计

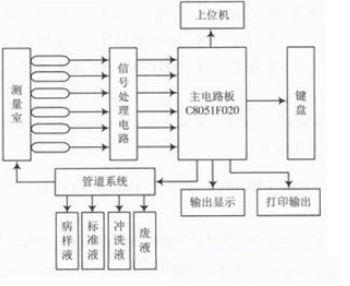

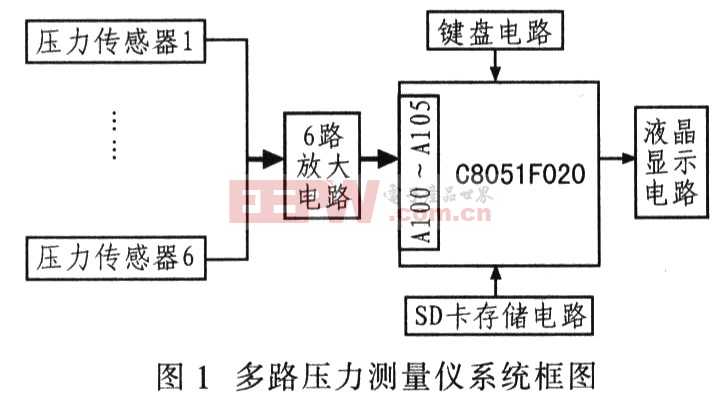

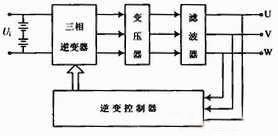

根据配电变压器终端产品所需实现的功能要求,以单片机C8051F020为核心的硬件结构如图1所示。

C8051F020简介

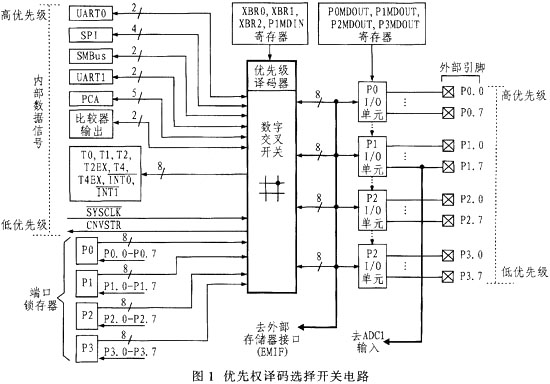

由于配电变压器监测终端需实现的功能较多,经反复比较,CPU选用C8051F020芯片。该芯片内置有64k Flash、4k RAM、1个SMBus/I2C、1个SPI、2个UART、5个定时器、64个通用I/O口、12位的ADC通道、电压基准(内部、外部)、温度传感器等。并具有以下特点:高速的50MIPS与8051 全兼容的微控制器内核。Flash 存储器可实现在线编程和用于非易失性数据存储(E2PROM 的作用),工作电压典型值为3V( 2.7V~3.3V),全部I/O、RST、JTAG 引脚均允许5V电压输入,工业级温度范围(-45 ~ +85)。片内JTAG 仿真电路提供全速非插入式(不使用在片资源)的电路内仿真支持断点、单步观察点、运行和停止等调试命令,支持存储器和寄存器校验和修改。

监控电路

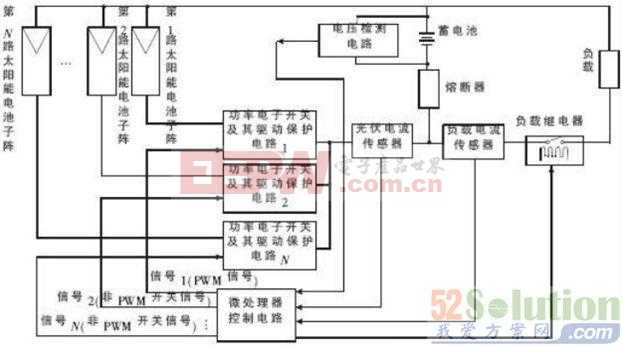

选用MAX706作为微处理器监控器,主要实现上电复位、监控程序运行和掉电检测功能。电路如图2所示。

MAX706可独立监视跟踪定时器输出。在1.6s内,如果CPU的P2.3脚电平不翻转,则/WDO脚输出低电平,通过/MR手动复位输入端使/RST脚产生复位信号,以防止由于干扰使CPU死机。设跳线器的目的是为了避免在下载程序和调试时MAX706产生复位信号。

VPP为电源的掉电检测信号,当电平降至5.5V以下时,/PFO输出低电平,使CPU进入中断程序进行掉电处理。CPU的P1.5脚被配置成外部中断输入,低电平触发。

日历时钟和存储电路

日历时钟芯片采用RTC4553,该芯片采用内置晶振和独特的数据方法,大大提高了时钟精度和可靠性。RTC4553配有串行外设通信接口,另有30

评论