杭州今朝体育设施工程有限公司选择我们,拥有4大优势

专业生产 专业技术人员

- 聘请国际体育工程专家和技术人员任公司技术顾问

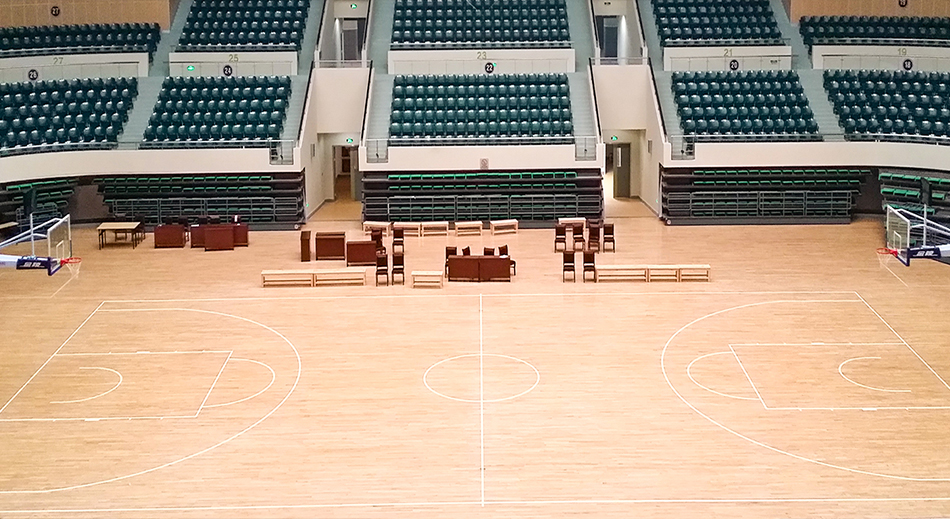

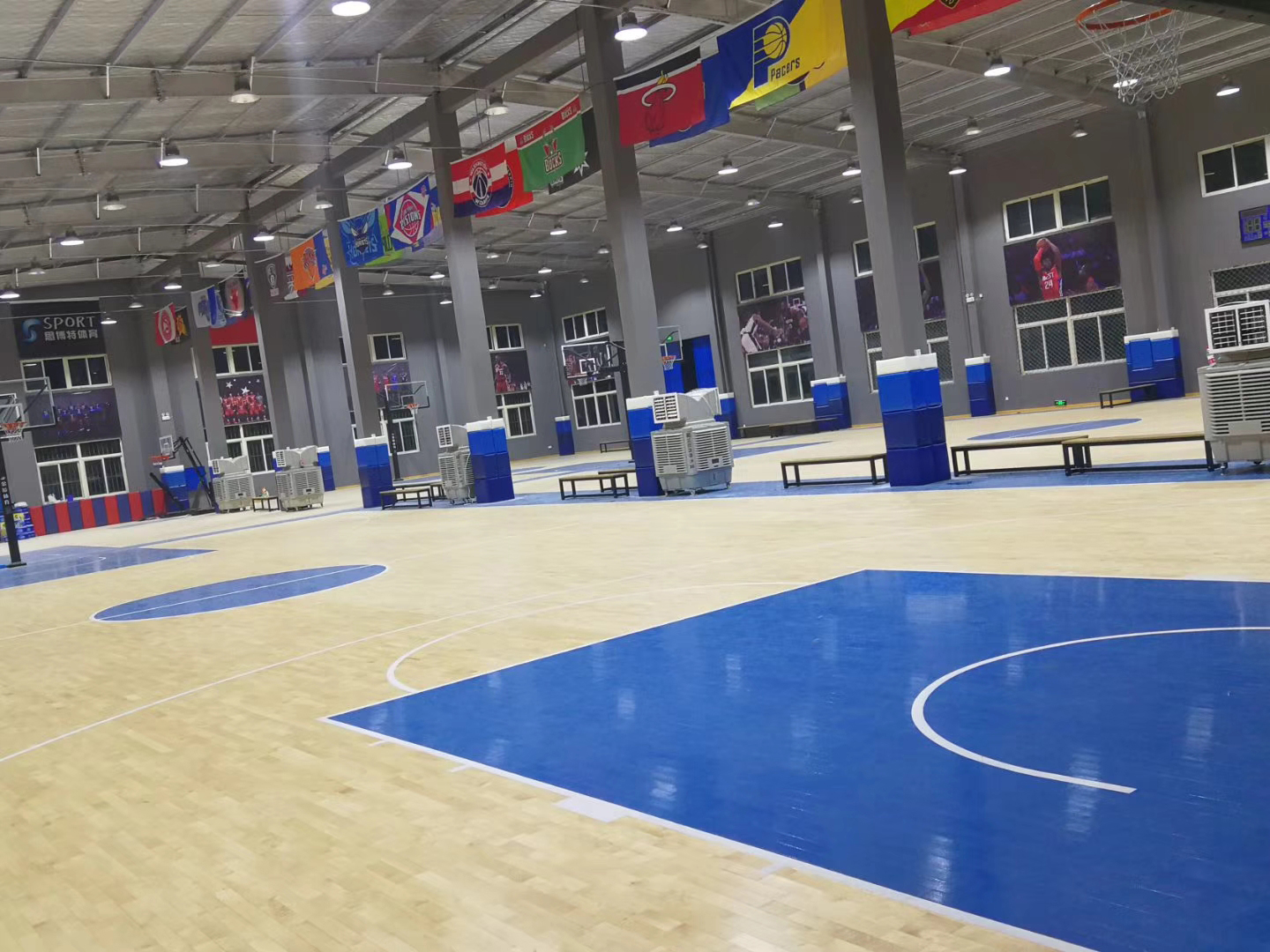

- 主要从事体育场馆设施设计、工程施工、场馆运营维护

- 主营体育运动地板、剧院舞台木地板等配套产品和服务

国际质量 质量保证

- 在黑龙江小兴安岭林区拥有自己的木地板生产工厂

- 通过ISO9001、ISO14001、GB/T28001三体系认证

- 年生产木地板10万平方米

精益求精 专业技术

- 不断引进国际体育工程设备

- 认证贯彻落实国际相关标准

- 秉承“用心、协作、敬业、创新”的企业精神

及时有效的售后支持 让您合作无忧

- 售后服务中心,有专业的售后服务团队

- 专业技术支持团队为用户提供解决方案

- 7*24小时贴心服务,快速响应客户售后问题