基于DDS的锁相频率合成器设计

1 引 言

现代频半合成源对频率精度、分辨率、转换时间和频谱纯度等指标提出了越来越高的要求。甚高频(VHF)频率合成器通常采用多锁相环路(PLL)结构,多环合成器将单环中的巨大分频比用多个环路来负担,同时各环,尤其足主环的鉴相频率大幅度提高,从而满足了鉴相频率高、分频比小和分辨率高等要求。但是由于多环组合的固有特性,尤其是分辨率每提高1个数量级,就要增加一级子环路,使得其频率转换速度低、线路复杂、可靠性差。

直接数字式频率合成技术(DDS)的频率分辨率高、频率转换速度快。DDS/PLL混合频率合成是一项新兴技术。DDS激励PLL倍频的方式能发挥DDS高分辨率的特点,但DDS信号中的相噪与杂散一旦落入环路内将会恶化lg N。

采用DDS内插PLL混频,即DDS输出与PLL反馈回路中的压控振荡器(VCO)输出混频,相当于用DDS取代多环频率台成器中的低(细)频率子环,电路结构简单,在频率转换速度、分辨率等方面性能优良,并且不存在DDS相噪与杂散恶化的问题。本文提出基于该思想的一种VHF段频率合成器设计。

2 方案设计

本方案设计一个VHF段频率合成器,输出信号频率分辨高,相位噪声低。

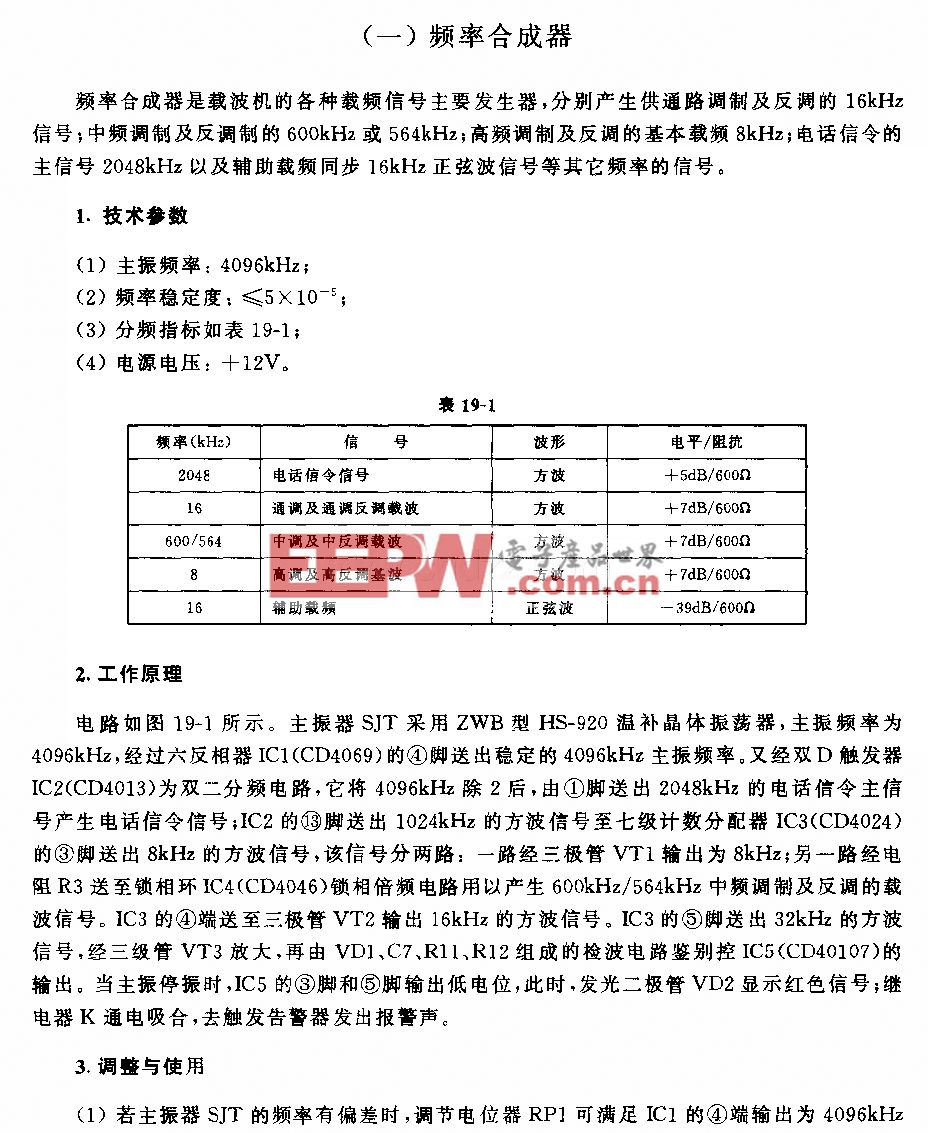

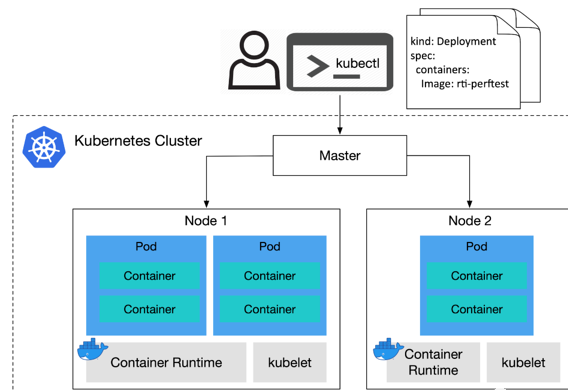

图1所示为频率合成器的原理框图。该合成器原理如下:压控振荡器(VCO)产生VHF段频率信号,在反馈通道中与直接数字式频率合成器(DDS)输出下混频,经带通滤波、程控分频器后送鉴相/鉴频器,与鉴相频率比较得到的相位误差信号,经低通环路滤波后,其平均值控制VCO输出向设定频率值靠拢并最终锁定。

本方案采用了DDS取代多环频率合成器中的低(细)频率子环,VCO输出频率范围89.6~110.4 MHz,DDS输出频率范围20~20.8 MHz,混频后取下变频69.6~89.6 MHz,经ECL预置分频器10分频至6.96~8.96 MHz,锁相环(PLL)鉴相频率取80 kHz,内部程控分频范围87~112 kHz。

压控振荡器输出频率和其他信号之间的关系由式(1)给出:

fOUT=N

分频器相关文章:分频器原理

评论