宽带中频数字接收机的FPGA实现

——

摘 要:本文提出了一种基于FPGA的宽带中频数字接收机的实现方法。

引言

在现代通信系统中,人们提出了各种各样的全数字调制解调方案,全数字接收机的研究则是其中的关键,其中正交解调技术由于可以实现信号相位和幅度信息的提取,因而越来越受到广泛的应用。

与其它几种解调方式相比QPSK调制方式抗噪声性能好,功率频谱段占用少,数据传输率高,是一种较好的调制方式。对于宽带、高载频的QPSK调制信号,如果用信号最高频率两倍以上的时钟采样,现有的器件根本无法满足要求,所以必须采用欠采样技术,降低系统对ADC器件和信号处理器件的性能要求。

现在大规模集成电路设计已经发展到在一片芯片上集成一个复杂系统的规模,所以单模块、单芯片的接收机不仅是可实现的,而且是一种必然趋势。用软件实现接收机解调功能并利用高速FPGA芯片,可以把整个接收机解调部分用单芯片实现;通过修改软件,可以改变接收机的功能,而且由于在软件、硬件上都是一个模块,可以方便的进行功能扩展以及与其它系统连接,这也符合软件无线电的思想。基于以上原因,在此提出一种单芯片FPGA实现的宽带中频数字接收机系统。

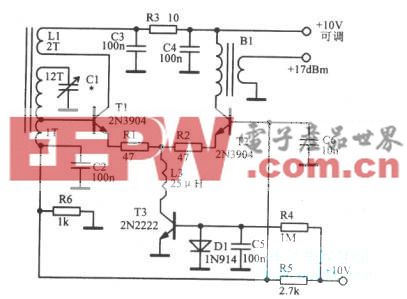

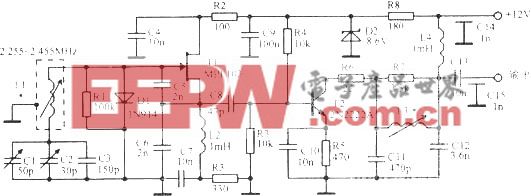

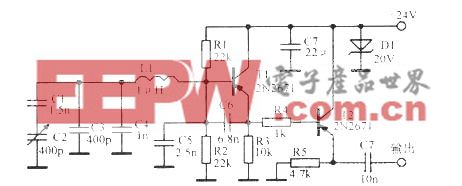

图1 中频数字接收机

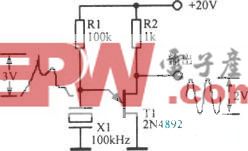

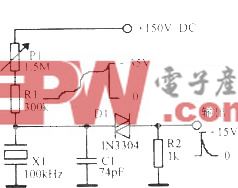

图2 NCO结构图

图3 解调器软件实现

系统结构

该接收机实现对载波频率70MHz、数据率9.856Mbps、最大载波频偏

评论